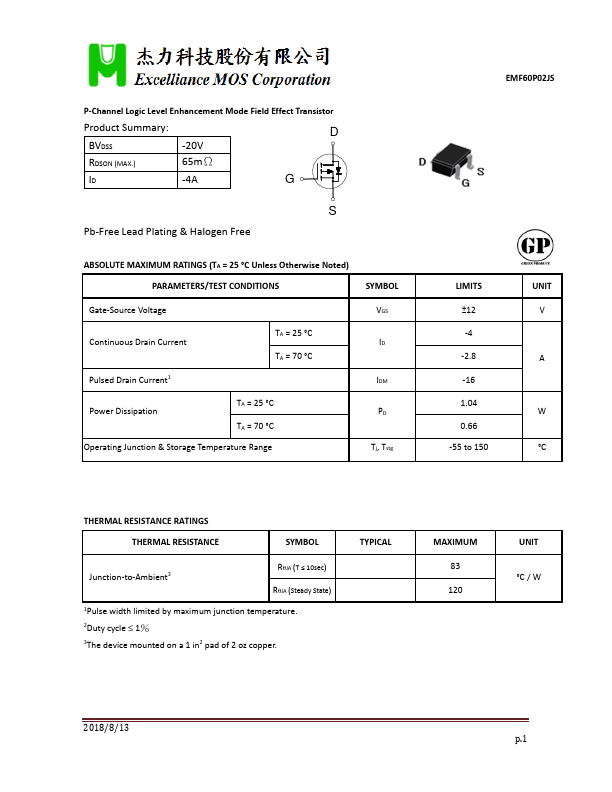

EMF60P02JS

EMF60P02JS is P-Channel Logic Level Enhancement Mode Field Effect Transistor manufactured by Excelliance MOS.

P-Channel Logic Level Enhancement Mode Field Effect Transistor

Product Summary:

BVDSS

-20V

RDSON (MAX.)

65mΩ

-4A

S Pb-Free Lead Plating & Halogen Free

ABSOLUTE MAXIMUM RATINGS (TA = 25 °C Unless Otherwise Noted) PARAMETERS/TEST CONDITIONS

SYMBOL

Gate-Source Voltage

Continuous Drain Current Pulsed Drain Current1

TA = 25 °C ID

TA = 70 °C

Power Dissipation

TA = 25 °C TA = 70 °C

Operating Junction & Storage Temperature Range

PD Tj, Tstg

LIMITS ±12 -4 -2.8 -16 1.04 0.66

-55 to 150

UNIT V

W °C

THERMAL RESISTANCE RATINGS THERMAL RESISTANCE

SYMBOL

Junction-to-Ambient3

RθJA (T ≤ 10sec) RθJA (Steady State)

1Pulse width limited by maximum junction temperature. 2Duty cycle ≤ 1% 3The device mounted on a 1 in2 pad of 2 oz copper.

TYPICAL

MAXIMUM 83 120

UNIT °C / W

2018/8/13 p.1

ELECTRICAL CHARACTERISTICS (TJ = 25 °C, Unless Otherwise Noted)

PARAMETER

SYMBOL...