74F174 Overview

Key Specifications

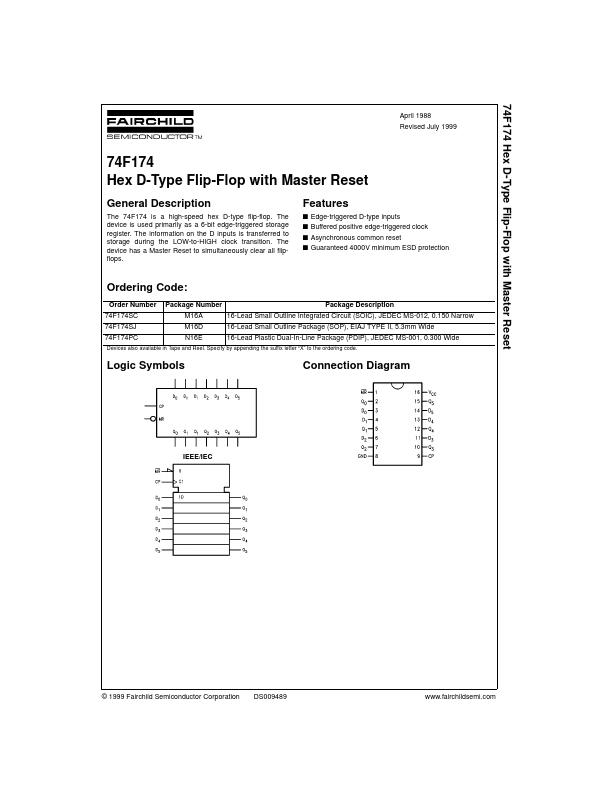

Package: DIP

Mount Type: Through Hole

Pins: 16

Operating Voltage: 5 V

Description

The 74F174 is a high-speed hex D-type flip-flop. The device is used primarily as a 6-bit edge-triggered storage register.

Key Features

- Specify by appending the suffix letter “X” to the ordering code