74LCXZ16245

74LCXZ16245 is Low Voltage 16-Bit Bidirectional Transceiver manufactured by Fairchild Semiconductor.

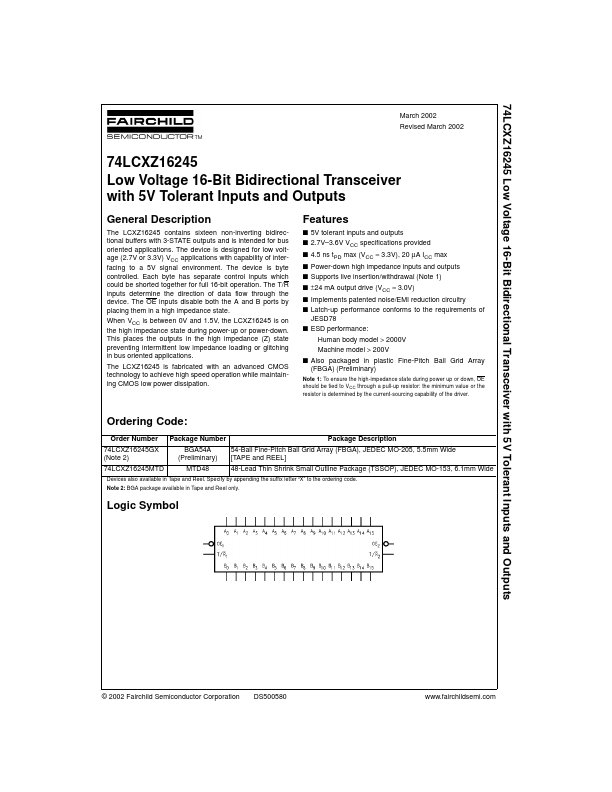

74LCXZ16245 Low Voltage 16-Bit Bidirectional Transceiver with 5V Tolerant Inputs and Outputs

March 2002 Revised March 2002

74LCXZ16245 Low Voltage 16-Bit Bidirectional Transceiver with 5V Tolerant Inputs and Outputs

General Description

The LCXZ16245 contains sixteen non-inverting bidirectional buffers with 3-STATE outputs and is intended for bus oriented applications. The device is designed for low voltage (2.7V or 3.3V) VCC applications with capability of interfacing to a 5V signal environment. The device is byte controlled. Each byte has separate control inputs which could be shorted together for full 16-bit operation. The T/R inputs determine the direction of data flow through the...