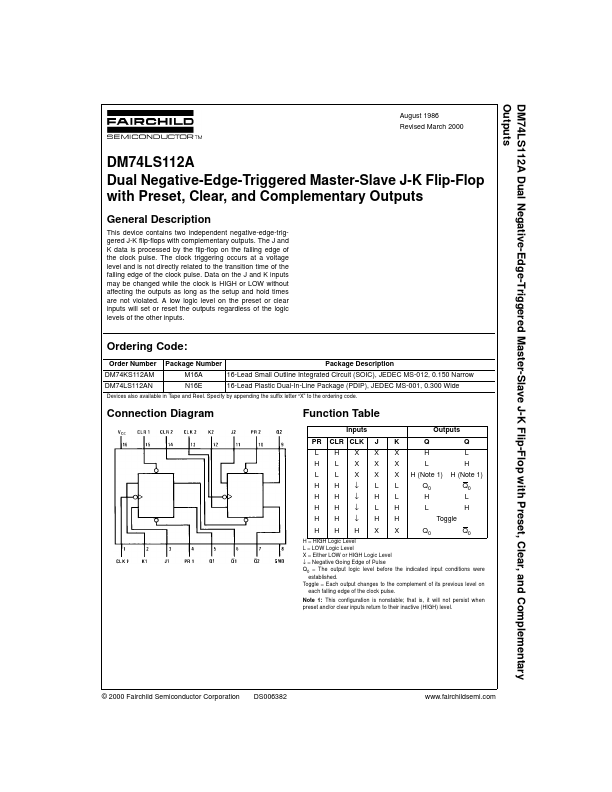

- Part: 74LS112A

- Description: Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop

- Manufacturer: Fairchild Semiconductor

- Size: 52.01 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| 74LS112A | Motorola Semiconductor | DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

| 74LS114A | Motorola Semiconductor | DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |