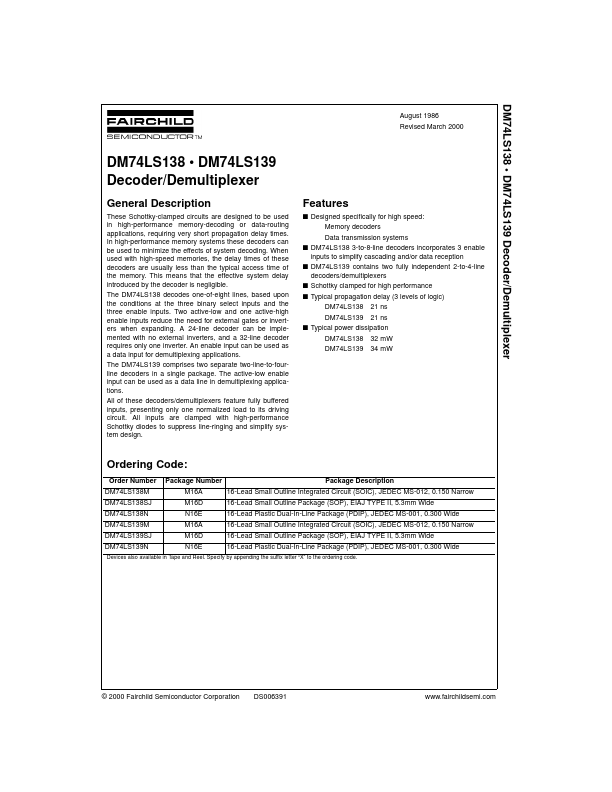

74LS138

Description

These Schottky-clamped circuits are designed to be used in high-performance memory-decoding or data-routing applications, requiring very short propagation delay times. In high-performance memory systems these decoders can be used to minimize the effects of system decoding.

Key Features

- C B A YO Y1 Y2 Y3 Y4 Y5 Y6 Y7 H H H H H L H H H H H H H H H H L H H H Logic Diagrams DM74LS138 DM74LS139 .fairchildsemi. 2 DM74LS138