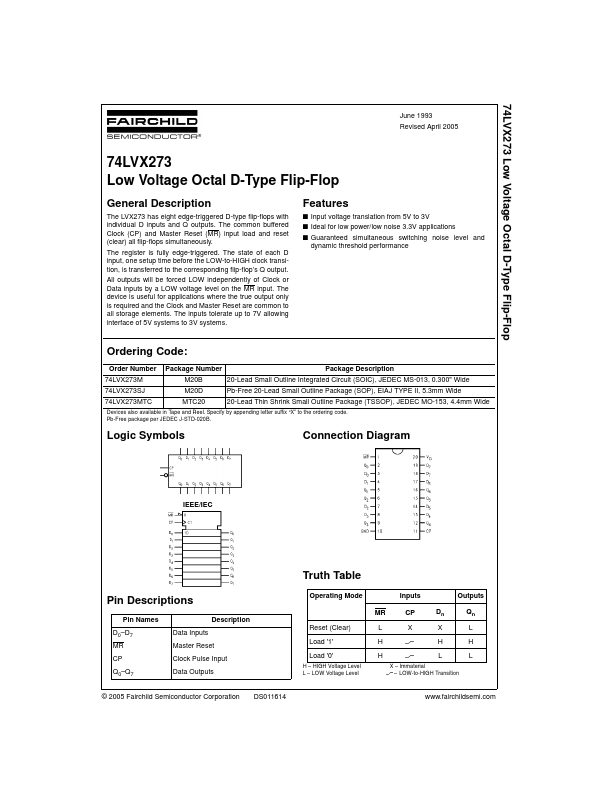

74LVX273 Description

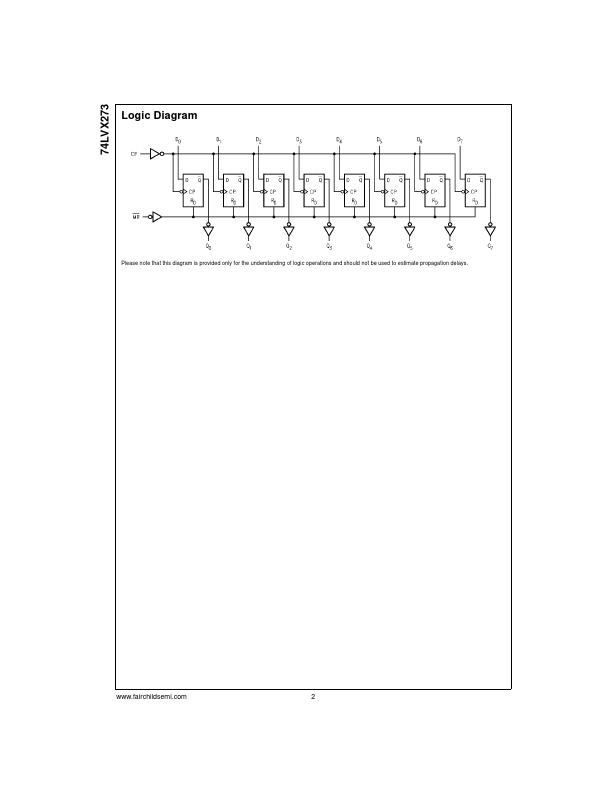

The LVX273 has eight edge-triggered D-type flip-flops with individual D inputs and Q outputs. The mon buffered Clock (CP) and Master Reset (MR) input load and reset (clear) all flip-flops simultaneously. The register is fully edge-triggered.