74VCX162601

74VCX162601 is Low Voltage 18-Bit Universal Bus Transceivers manufactured by Fairchild Semiconductor.

- Part of the 74VCX comparator family.

- Part of the 74VCX comparator family.

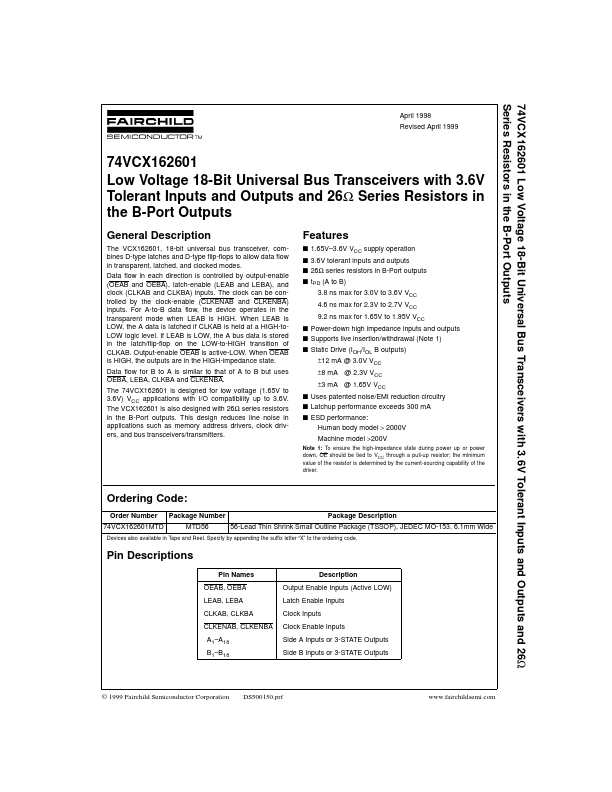

74VCX162601 Low Voltage 18-Bit Universal Bus Transceivers with 3.6V Tolerant Inputs and Outputs and 26Ω Series Resistors in the B-Port Outputs

April 1998 Revised April 1999

74VCX162601 Low Voltage 18-Bit Universal Bus Transceivers with 3.6V Tolerant Inputs and Outputs and 26Ω Series Resistors in the B-Port Outputs

General Description

The VCX162601, 18-bit universal bus transceiver, bines D-type latches and D-type flip-flops to allow data flow in transparent, latched, and clocked modes. Data flow in each direction is controlled by output-enable (OEAB and OEBA), latch-enable (LEAB and LEBA), and clock (CLKAB and CLKBA) inputs. The clock can be controlled by the clock-enable (CLKENAB and...