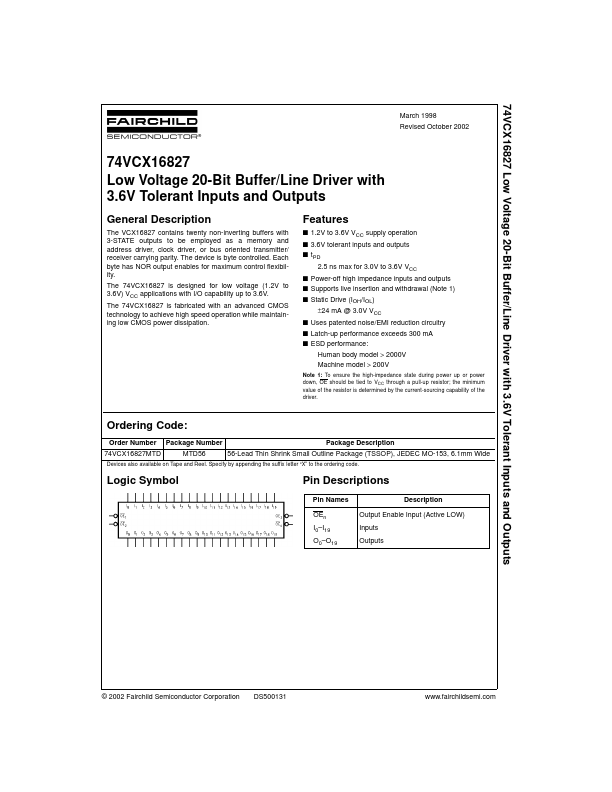

74VCX16827 Description

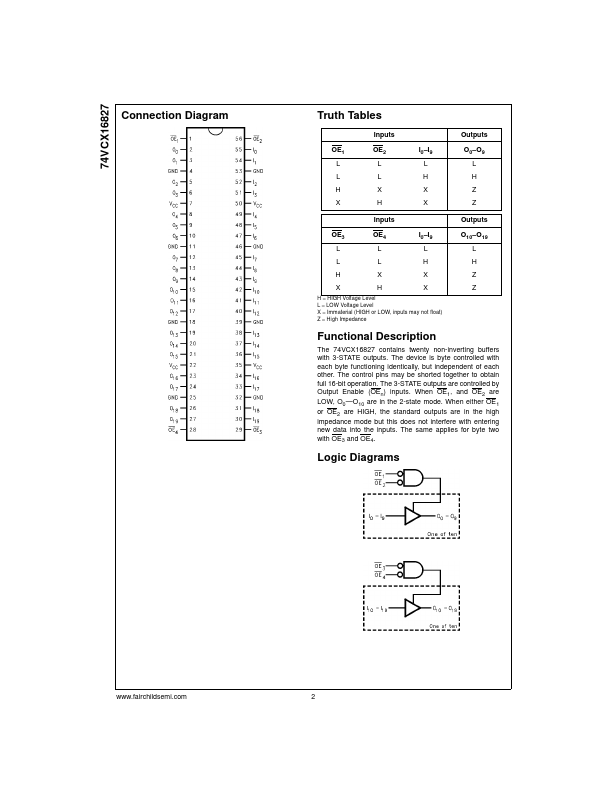

The VCX16827 contains twenty non-inverting buffers with 3-STATE outputs to be employed as a memory and address driver, clock driver, or bus oriented transmitter/ receiver carrying parity. The device is byte controlled. Each byte has NOR output enables for maximum control flexibility.