Datasheet Summary

74VHC112 Dual J-K Flip-Flops with Preset and Clear

74VHC112 Dual J-K Flip-Flops with Preset and Clear

May 2007 tm

Features

- High speed: fMAX = 200MHz (Typ.) at VCC = 5.0V

- Low power dissipation: ICC = 2µA (Max.) at TA = 25°C

- High noise immunity: VNIH = VNIL = 28% VCC (Min.)

- Power down protection is provided on all inputs

- Pin and function patible with 74HC112

General Description

The VHC112 is an advanced high speed CMOS device fabricated with silicon gate CMOS technology. It achieves the high-speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation.

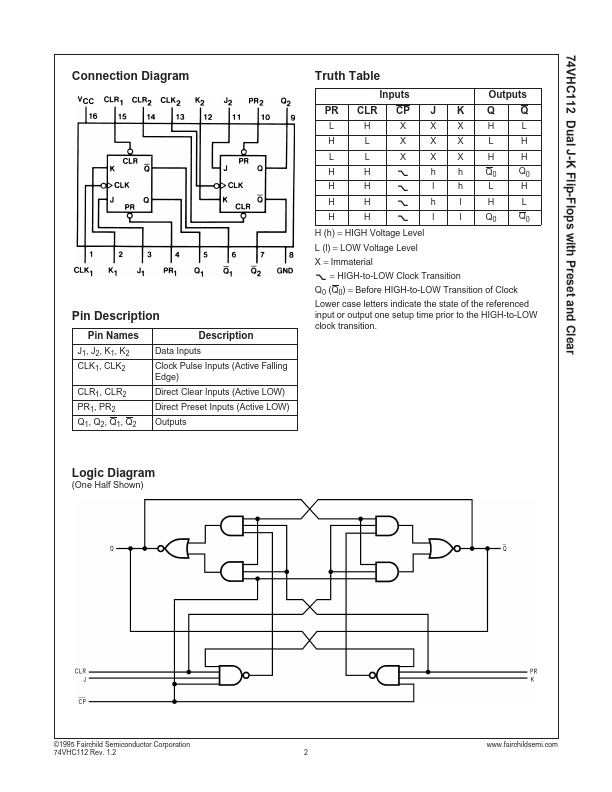

The VHC112 contains two independent, high-speed JK flip-flops with Direct Set...