DM74LS166

Description

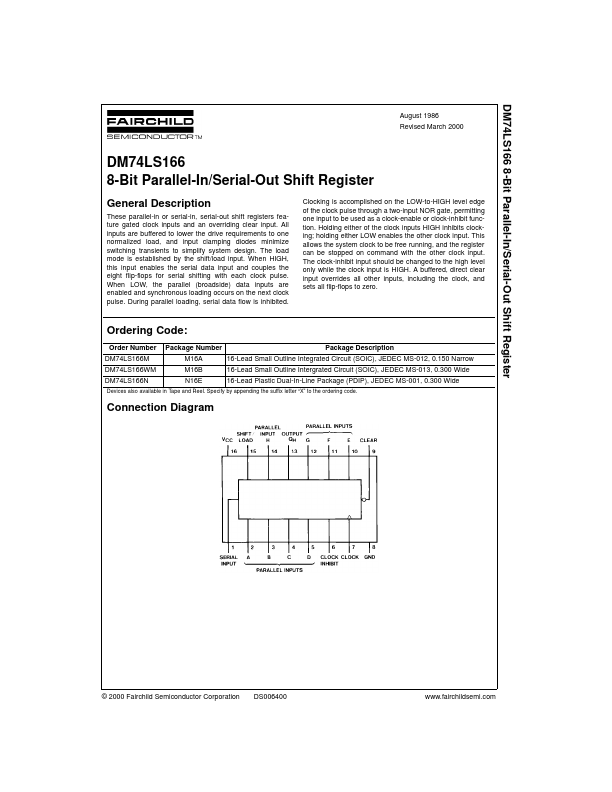

These parallel-in or serial-in, serial-out shift registers feature gated clock inputs and an overriding clear input.

Key Features

- gated clock inputs and an overriding clear input

- The load mode is established by the shift/load input

- When HIGH, this input enables the serial data input and couples the eight flip-flops for serial shifting with each clock pulse

- When LOW, the parallel (broadside) data inputs are enabled and synchronous loading occurs on the next clock pulse

- During parallel loading, serial data flow is inhibited

- Holding either of the clock inputs HIGH inhibits clocking; holding either LOW enables the other clock input

- This allows the system clock to be free running, and the register can be stopped on mand with the other clock input

- The clock-inhibit input should be changed to the high level only while the clock input is HIGH

- A buffered, direct clear input overrides all other inputs, including the clock, and sets all flip-flops to zero

- Specify by appending the suffix letter “X” to the ordering code