FIN1026 Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 14

Operating Voltage: 3.3 V

Description

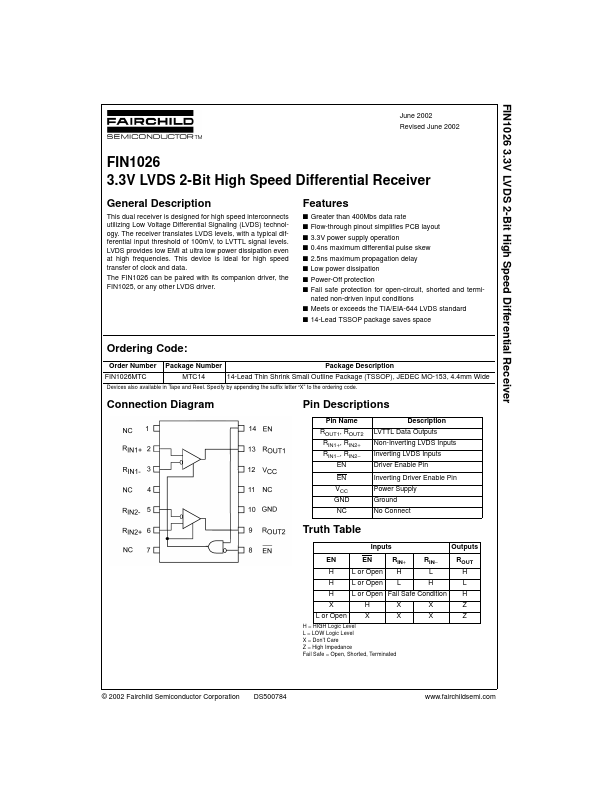

This dual receiver is designed for high speed interconnects utilizing Low Voltage Differential Signaling (LVDS) technology. The receiver translates LVDS levels, with a typical differential input threshold of 100mV, to LVTTL signal levels.

Key Features

- Specify by appending the suffix letter “X” to the ordering code