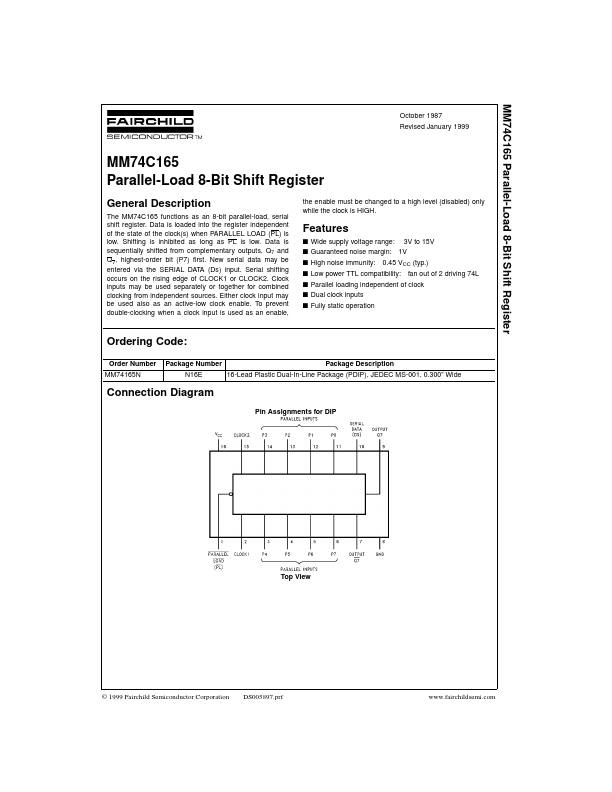

| Part | MM74C165 |

|---|---|

| Description | Parallel-Load 8-Bit Shift Register |

| Manufacturer | Fairchild Semiconductor |

| Size | 50.96 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MM74C165 | National Semiconductor | Parallel-Load 8-Bit Shift Register |

| MM74C160 | National Semiconductor | Decade Counter with Asynchronous Clear |

| MM74C162 | National Semiconductor | Decade Counter with Asynchronous Clear |

| MM74C163 | National Semiconductor | Decade Counter with Asynchronous Clear |

| MM74C161 | National Semiconductor | Decade Counter with Asynchronous Clear |