MM74HC139 Overview

Description

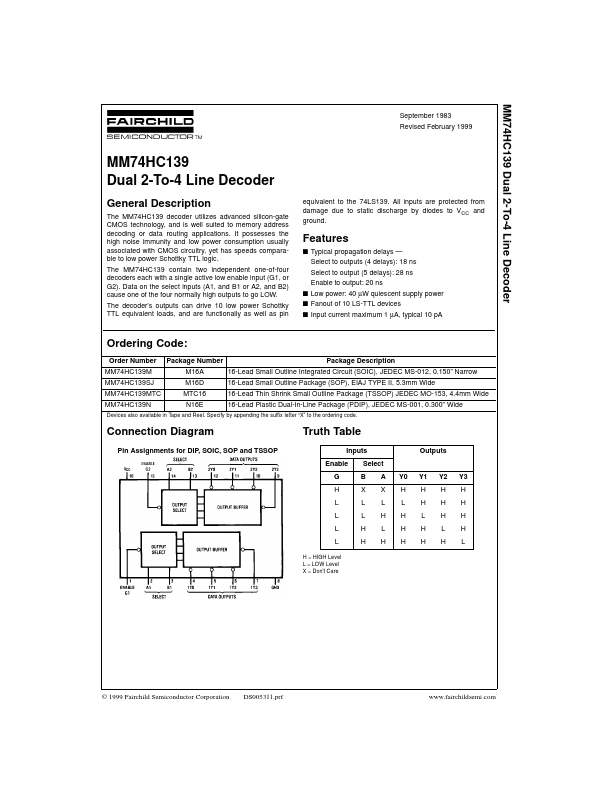

The MM74HC139 decoder utilizes advanced silicon-gate CMOS technology, and is well suited to memory address decoding or data routing applications. It possesses the high noise immunity and low power consumption usually associated with CMOS circuitry, yet has speeds comparable to low power Schottky TTL logic.

Key Features

- Specify by appending the suffix letter “X” to the ordering code