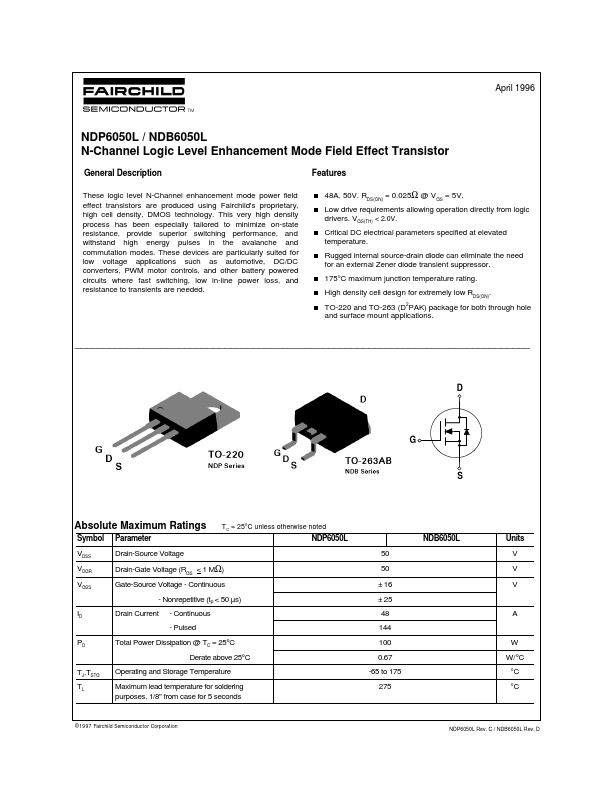

NDP6050L

Key Features

- RDS(ON) = 0.025Ω @ VGS = 5V

- Low drive requirements allowing operation directly from logic drivers

- Critical DC electrical parameters specified at elevated temperature

- Rugged internal source-drain diode can eliminate the need for an external Zener diode transient suppressor

- 175°C maximum junction temperature rating