NM25C640

NM25C640 is 64K-Bit Serial CMOS EEPROM (Serial Peripheral Interface (SPI) Synchronous Bus) manufactured by Fairchild Semiconductor.

NM25C640 64K-Bit Serial CMOS EEPROM (Serial Periphrial Interface (SPI) Synchronous Bus)

PRELIMINARY

March 1999

NM25C640 64K-Bit Serial CMOS EEPROM (Serial Peripheral Interface (SPI) Synchronous Bus)

General Description

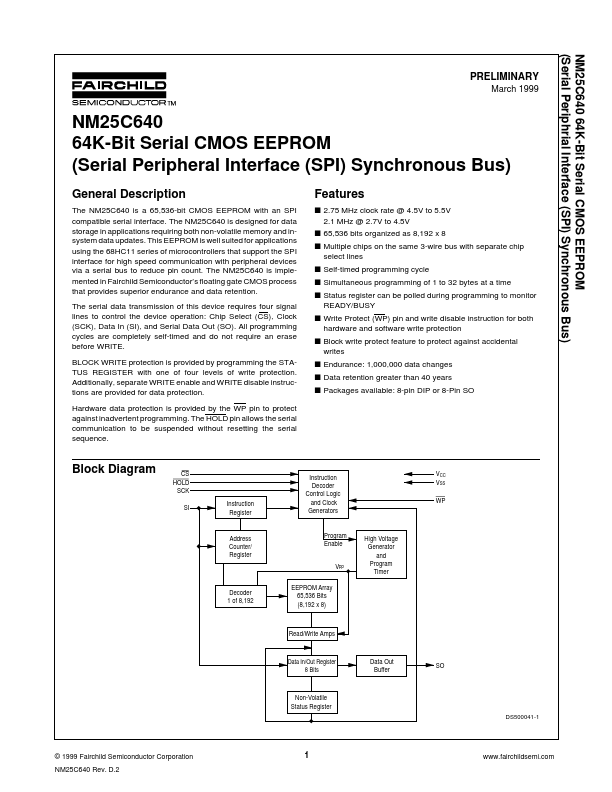

The NM25C640 is a 65,536-bit CMOS EEPROM with an SPI patible serial interface. The NM25C640 is designed for data storage in applications requiring both non-volatile memory and insystem data updates. This EEPROM is well suited for applications using the 68HC11 series of microcontrollers that support the SPI interface for high speed munication with peripheral devices via a serial bus to reduce pin count. The NM25C640 is implemented in Fairchild Semiconductor’s floating gate CMOS process that provides superior endurance and data retention. The serial data transmission of this device requires four signal lines to control the device operation: Chip Select (CS), Clock (SCK), Data In (SI), and Serial Data Out (SO). All programming cycles are pletely self-timed and do not require an erase before WRITE. BLOCK WRITE protection is provided by programming the STATUS REGISTER with one of four levels of write protection. Additionally, separate WRITE enable and WRITE disable instructions are provided for data protection. Hardware data protection is provided by the WP pin to protect against inadvertent programming. The HOLD pin allows the serial munication to be suspended without resetting the serial sequence.

Features s 2.75 MHz clock rate @ 4.5V to 5.5V 2.1 MHz @ 2.7V to 4.5V s 65,536 bits organized as 8,192 x 8 s Multiple chips on the same 3-wire bus with separate chip select lines s Self-timed programming cycle s Simultaneous programming of 1 to 32 bytes at a time s Status register can be polled during programming to monitor READY/BUSY s Write Protect (WP) pin and write disable instruction for both hardware and software write protection s Block write protect feature to protect against accidental writes s Endurance: 1,000,000 data changes s Data...