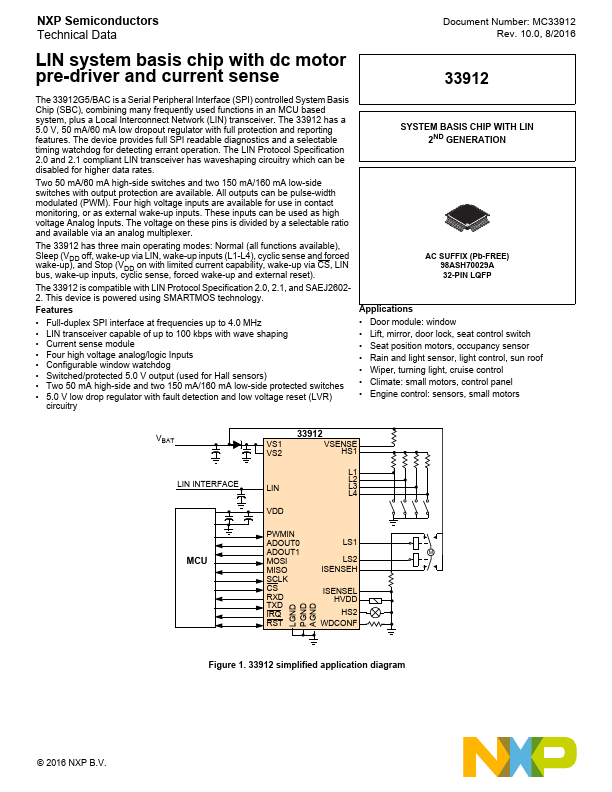

MC33912 Overview

Key Specifications

Package: LQFP

Mount Type: Surface Mount

Pins: 32

Operating Voltage: 13.5 V

Key Features

- The device provides full SPI readable diagnostics and a selectable timing watchdog for detecting errant operation

- The LIN Protocol Specification 2.0 and 2.1 compliant LIN transceiver has waveshaping circuitry which can be disabled for higher data rates

- Two 50 mA/60 mA high-side switches and two 150 mA/160 mA low-side switches with output protection are available

- All outputs can be pulse-width modulated (PWM)

- Four high voltage inputs are available for use in contact monitoring, or as external wake-up inputs