Datasheet Summary

Freescale Semiconductor Data Sheet: Advance Information

Document Number: MCF52277 Rev. 6, 07/2008

LQFP- 176 24 mm x 24 mm MAPBGA- 196 15mm x 15mm

MCF5227x ColdFire® Microprocessor Data Sheet

..

Features

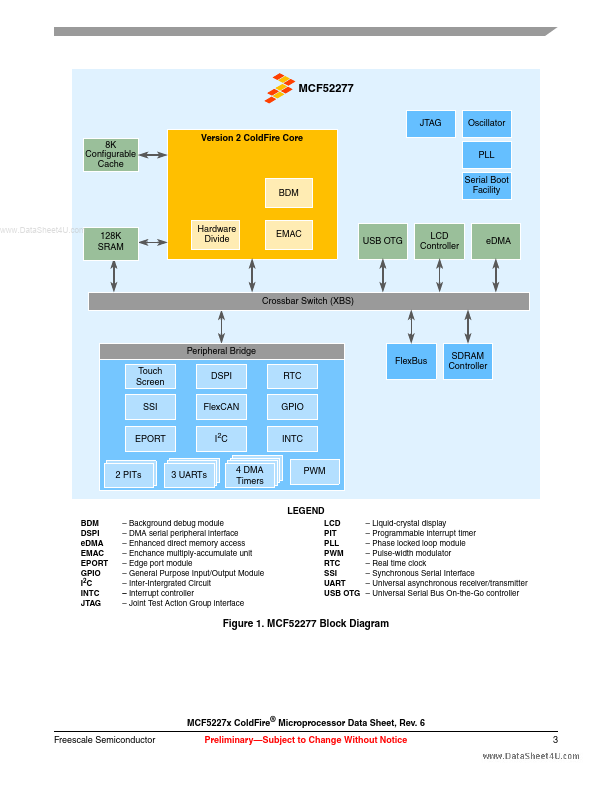

- Version 2 ColdFire® Core with EMAC

- Up to 159 Dhrystone 2.1 MIPS @ 166.67 MHz

- 8 Kbytes configurable cache (instruction only, data only, or split instruction/data)

- 128 Kbytes internal SRAM

- Support for booting from SPI-patible flash, EEPROM, and FRAM devices

- Crossbar switch technology (XBS) for concurrent access to peripherals or RAM from multiple bus masters

- 16 channel DMA controller

- 16- or 32-bit SDR/DDR controller

- USB 2.0 On-the-Go controller

-...