MB91F233L

Overview

- 32-bit RISC, load/store architecture with a 5 stage pipeline

- Maximum operating frequency: 33.6 MHz (oscillation frequency = 4.2 MHz, oscillation frequency 8-multiplier (PLL clock multiplication method) )

- 16-bit fixed length instructions (basic instructions)

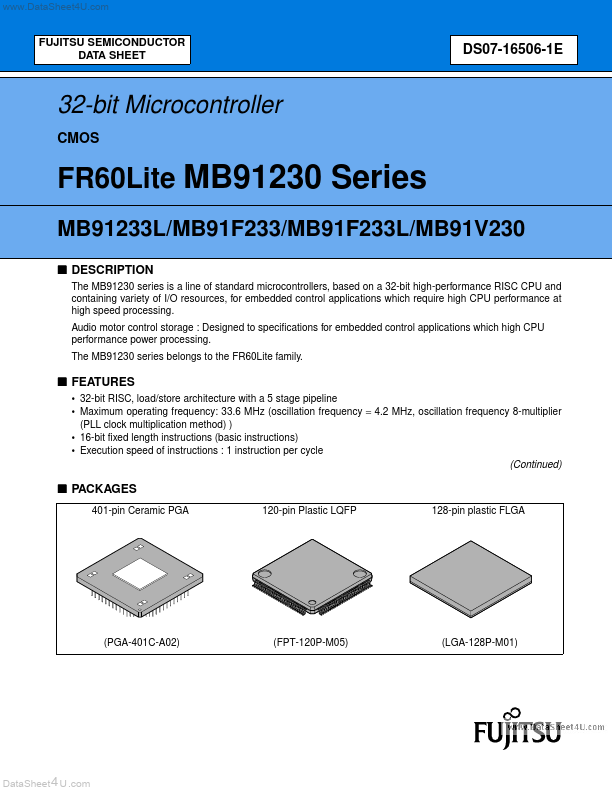

- Execution speed of instructions : 1 instruction per cycle (Continued) s PACKAGES 401-pin Ceramic PGA 120-pin Plastic LQFP 128-pin plastic FLGA (PGA-401C-A02) (FPT-120P-M05) (LGA-128P-M01) DataSheet 4 U .com MB91230 Series (Continued)

- Memory-to-memory transfer, bit handling, and barrel shift instructions, etc. : Instructions suitable for embedded applications

- Function entry/exit instructions, multiple-register load/store instructions : Instructions adapted for C-language

- Register interlock function : Facilitates coding in assembler

- Built-in multiplier with instruction-level support - 32-bit multiplication with sign : 5 cycles - 16-bit multiplication with sign : 3 cycles

- Interrupt (PC and PS save) : 6 cycles (16 priority levels)

- Harvard architecture allowing program access and data access to be executed simultaneously