CDP1802BC

Key Features

- Minimum instruction fetch-execute time of 3.2 /.IS (maximum clock frequency =5 MHz) at Voo =5 V

- Any bination of standard RAM and ROM up to 65,536 bytes

- Operates with slow memories, up to 775 ns access time at fCl = 5 MHz

- B-bit parallel organization with bidirectional data bus and multiplexed address bus

- 16 x 16 matrix of registers for use as multiple program counters, data pointers, or data registers

- On-chip DMA, interrupt, and flag mputs

- Programmable single-bit output port

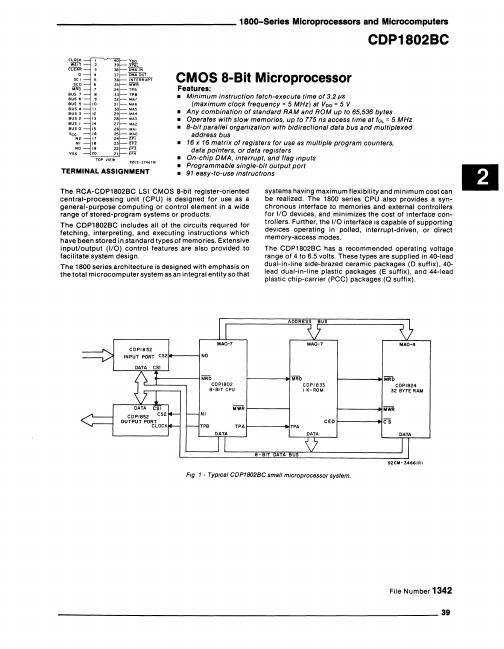

- 91 easy-to-use instructIOns The RCA-COP1802BC LSI CMOS 8-bit register-oriented c