GS82032AT

GS82032AT is 2Mb Synchronous Burst SRAM manufactured by GSI Technology.

Discontinued Product

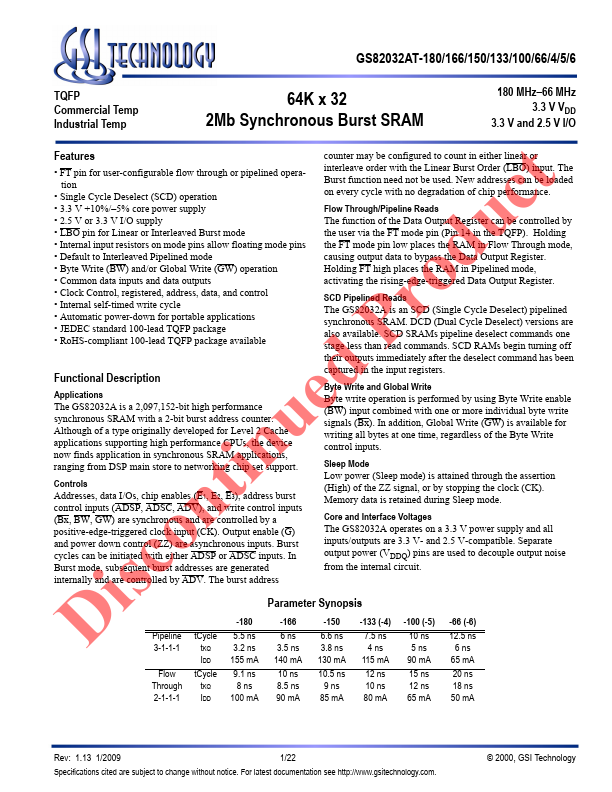

GS82032AT-180/166/150/133/100/66/4/5/6

TQFP mercial Temp Industrial Temp

64K x 32 2Mb Synchronous Burst SRAM

180 MHz- 66 MHz 3.3 V VDD

3.3 V and 2.5 V I/O

Features

- FT pin for user-configurable flow through or pipelined operation

- Single Cycle Deselect (SCD) operation

- 3.3 V +10%/- 5% core power supply

- 2.5 V or 3.3 V I/O supply

- LBO pin for Linear or Interleaved Burst mode

- Internal input resistors on mode pins allow floating mode pins

- Default to Interleaved Pipelined mode

- Byte Write (BW) and/or Global Write (GW) operation

- mon data inputs and data outputs

- Clock Control, registered, address, data, and control

- Internal self-timed write cycle

- Automatic power-down for portable applications

- JEDEC standard 100-lead TQFP package

- Ro HS-pliant 100-lead TQFP package available

Functional Description

Applications The GS82032A is a 2,097,152-bit high performance synchronous SRAM with a 2-bit burst address...