GS8322Z18 Overview

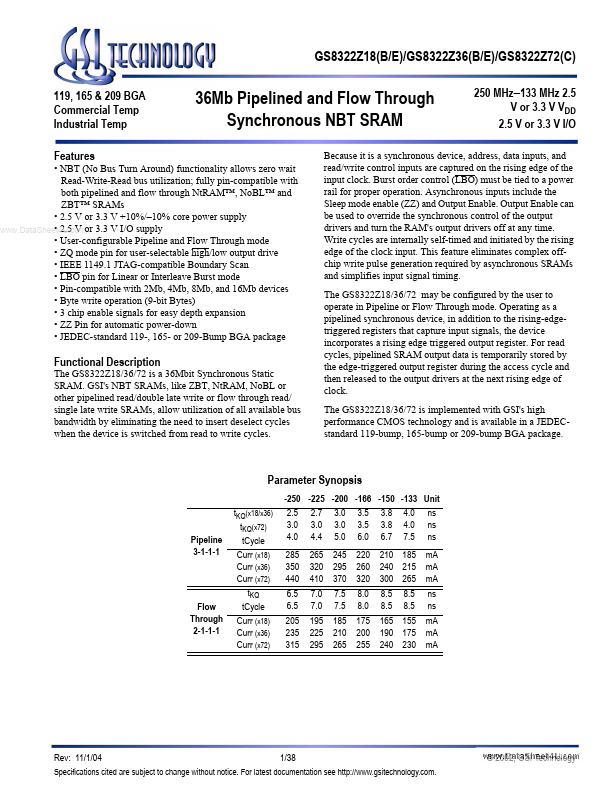

Key Specifications

Package: FBGA

Operating Voltage: 2.5 V

Max Voltage (typical range): 2.7 V

Min Voltage (typical range): 2.3 V

Key Features

- 2.5 V or 3.3 V +10%/–10% core power supply

- 2.5 V or 3.3 V I/O supply

- User-configurable Pipeline and Flow Through mode

- ZQ mode pin for user-selectable high/low output drive

- IEEE 1149.1 JTAG-compatible Boundary Scan

- LBO pin for Linear or Interleave Burst mode

- Pin-compatible with 2Mb, 4Mb, 8Mb, and 16Mb devices

- 3 chip enable signals for easy depth expansion

- ZZ Pin for automatic power-down