HD74CDC857 Key Features

- Supports 100 MHz to 150 MHz operation range -1

- Distributes one differential clock input pair to ten differential clock outputs pairs

- SSTL_2 (Stub Series Terminated Logic) differential inputs and LVCMOS reset (G) input

- Supports spread spectrum clock

- External feedback pins (FBIN, FBIN) are used to synchronize the outputs to the clock input

- Supports both 3.3 V/2.5V analog supply voltage (AV CC), and 2.5 V VDDQ

- No external RC network required

- Sleep mode detection

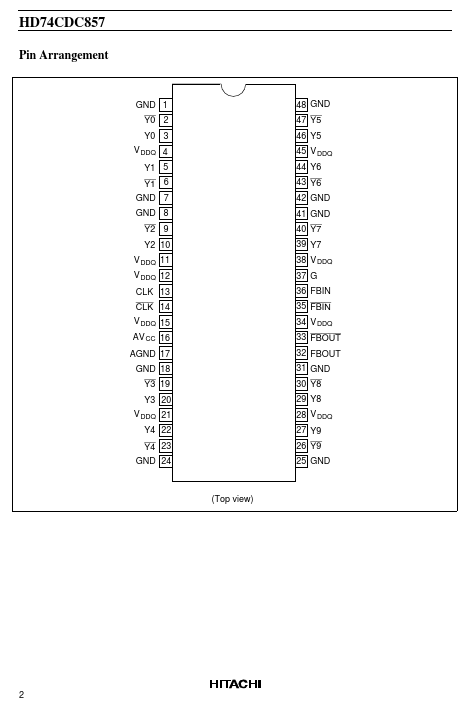

- 48pin TSSOP (Thin Shrink Small Outline Package) Note: 1. 200 MHz (Max) ver. will be available by 4Q/’99