HD74HC112

Description

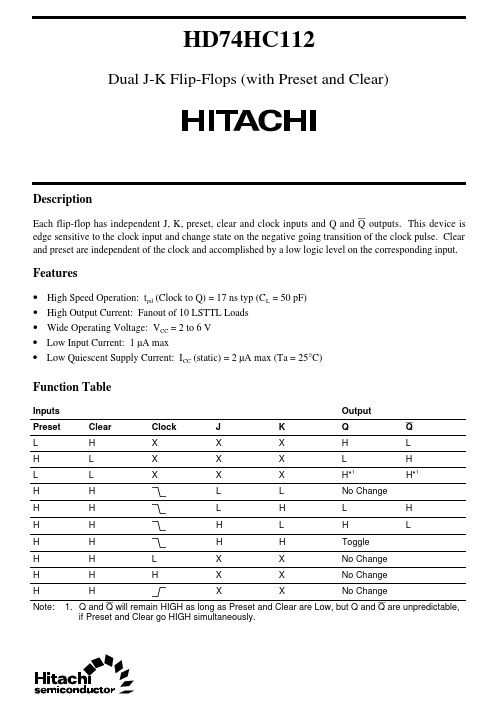

Each flip-flop has independent J, K, preset, clear and clock inputs and Q and Q outputs. This device is edge sensitive to the clock input and change state on the negative going transition of the clock pulse.

Key Features

- High Speed Operation: tpd (Clock to Q) = 17 ns typ (CL = 50 pF) High Output Current: Fanout of 10 LSTTL Loads Wide Operating Voltage: VCC = 2 to 6 V Low Input Current: 1 µA max Low Quiescent Supply Current: ICC (static) = 2 µA max (Ta = 25°C)