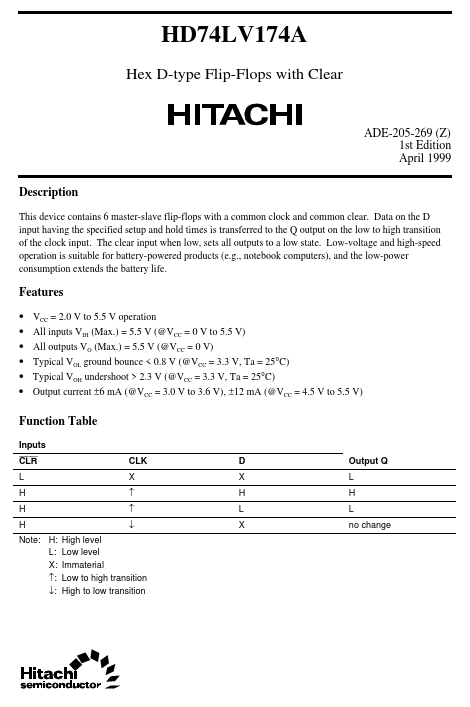

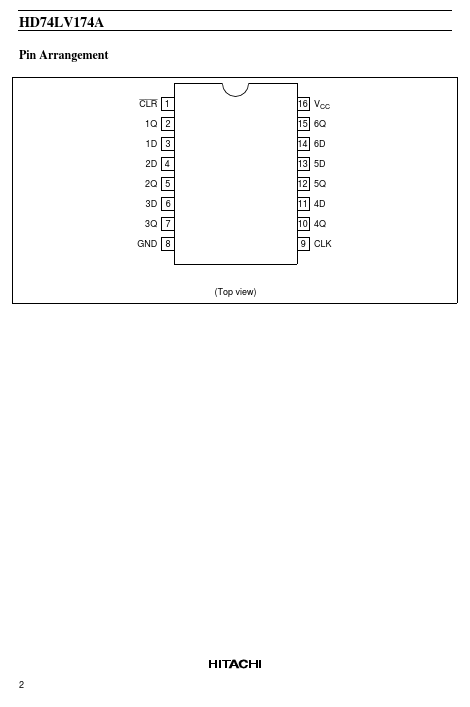

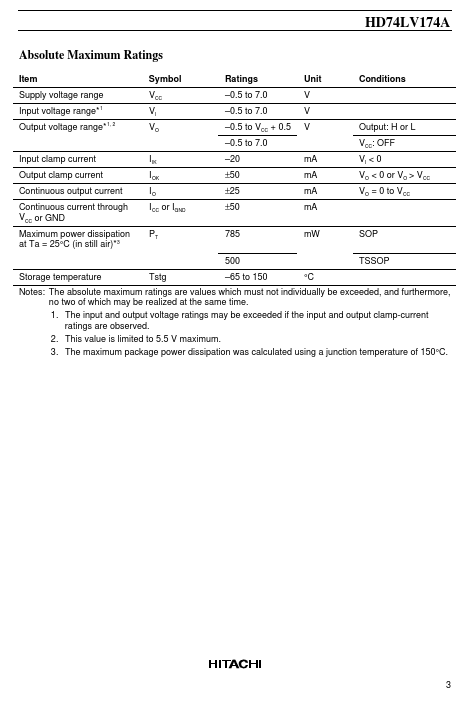

- Part: HD74LV174A

- Description: Hex D-type Flip-Flops with Clear

- Manufacturer: Hitachi Semiconductor

- Size: 64.01 KB

Related Hitachi Semiconductor Datasheets

| Part Number | Description |

|---|---|

| HD74LV175A | Quad. D-type Flip-Flops with Clear |

| HD74LV10A | Triple 3-input Positive NAND Gates |

| HD74LV11A | Triple 3-input Positive AND Gates |

| HD74LV123A | Dual Retriggerable Monostable Multivibrators |

| HD74LV125A | Quad. Bus Buffer Gates with 3-state Outputs |