HD74LVC16373A

HD74LVC16373A is 16-bit D-type Transparent Latches with 3-state Outputs manufactured by Hitachi Semiconductor.

Description

The HD74LVC16373A has sixteen D type latches with three state outputs in a 48 pin package. When the latch enable input is high, the Q outputs will follow the D inputs. When the latch enable goes low, data at the D inputs will be retained at the outputs until latch enable returns high again. When a high logic level is applied to the output control input (1 G, 2G), all outputs go to a high impedance state, regardless of what signals are present at the other inputs and the state of the storage elements. Low voltage and high speed operation is suitable at the battery drive product (note type personal puter) and low power consumption extends the life of a battery for long time operation.

Features

- -

- -

- - VCC = 2.0 V to 5.5 V All inputs VIH (Max.) = 5.5 V (@VCC = 0 V to 5.5 V) All outputs VOUT (Max.) = 5.5 V (@VCC = 0 V or output off state) Typical VOL ground bounce < 0.8 V (@VCC = 3.3 V, Ta = 25°C) Typical VOH undershoot > 2.0 V (@VCC = 3.3 V, Ta = 25°C) High output current ±24 m A (@VCC = 3.0 V to 5.5 V)

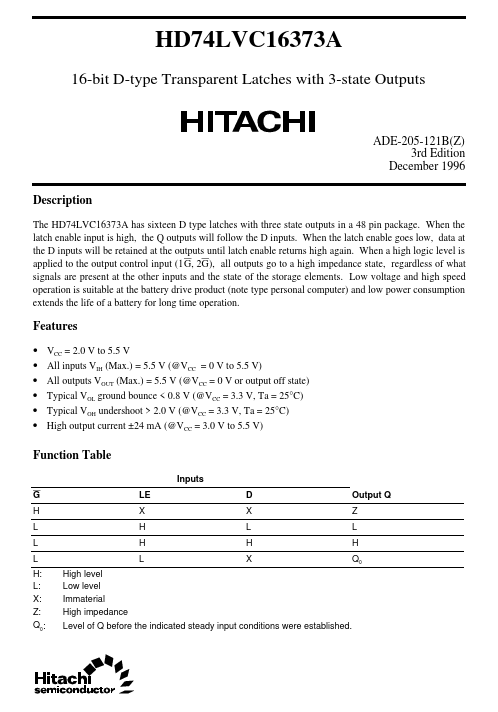

Function Table

Inputs G H L L L H: L: X: Z: Q0: LE X H H L D X L H X Output Q Z L H Q0

High level Low level Immaterial High impedance Level of Q before the indicated steady input conditions were established.

Pin Arrangement

1G 1 1Q1 2 1Q2 3 GND 4 1Q3 5 1Q4 6 VCC 7 1Q5 8 1Q6 9 GND 10 1Q7 11 1Q8 12 2Q1 13 2Q2 14 GND 15 2Q3 16 2Q4 17 VCC 18 2Q5 19 2Q6 20 GND 21 2Q7 22 2Q8 23 2G 24

G Q G Q D D G Q G Q G Q G Q G Q G Q G Q G Q G Q G Q G Q G Q G Q G Q D D

48 1LE 47 1D1 46 1D2 45 GND

44 1D3 43 1D4 42 VCC

41 1D5 40 1D6 39 GND 38 1D7 37 1D8 36 2D1 35 2D2 34 GND 33 2D3 32 2D4 31 VCC 30 2D5 29 2D6 28 GND 27 2D7 26 2D8 25 2LE

(Top view)

Absolute Maximum Ratings

Item Supply voltage Input diode current Input voltage Output diode current Symbol VCC I IK VI I OK Ratings

- 0.5 to 6.0

- 50

- 0.5 to 6.0

- 50 50 Output voltage VO

- 0.5 to VCC +0.5

- 0.5 to 6.0 Output current VCC, GND current / pin Storage...