HM5225325F-B60

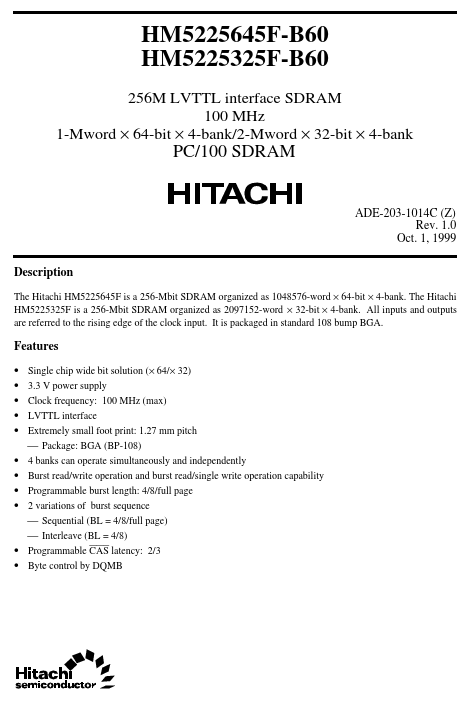

HM5225325F-B60 is 256M LVTTL interface SDRAM 100 MHz 1-Mword x 64-bit x 4-bank/2-Mword x 32-bit x 4-bank PC/100 SDRAM manufactured by Hitachi Semiconductor.

Description

The Hitachi HM5225645F is a 256-Mbit SDRAM organized as 1048576-word × 64-bit × 4-bank. The Hitachi HM5225325F is a 256-Mbit SDRAM organized as 2097152-word × 32-bit × 4-bank. All inputs and outputs are referred to the rising edge of the clock input. It is packaged in standard 108 bump BGA.

Features

- -

- -

- -

- -

- Single chip wide bit solution (× 64/× 32) 3.3 V power supply Clock frequency: 100 MHz (max) LVTTL interface Extremely small foot print: 1.27 mm pitch Package: BGA (BP-108) 4 banks can operate simultaneously and independently Burst read/write operation and burst read/single write operation capability Programmable burst length: 4/8/full page 2 variations of burst sequence Sequential (BL = 4/8/full page) Interleave (BL = 4/8) Programmable CAS latency: 2/3 Byte control by DQMB

- -

HM5225645F-B60, HM5225325F-B60

- Refresh cycles: 4096 refresh cycles/64 ms

- 2 variations of refresh Auto refresh Self refresh

- Full page burst length capability Sequential burst Burst stop capability

Ordering Information

Type No. HM5225645FBP-B60- HM5225325FBP-B60- Frequency 100 MHz 100 MHz CAS latency 3 3 Package 14 mm × 22 mm 108 bump BGA (BP-108)

Note: 66 MHz operation at CAS latency = 2.

HM5225645F-B60, HM5225325F-B60

Pin Arrangement (HM5225645F)

108-bump BGA 1 A B C D E F G H J K L

DQ63

DQ62

DQ49

DQ48

DQ47

DQ46

DQ33

DQ32

DQ61

DQ60

DQ51

DQ50...