H5TQ2G83BFR-xxJ

Overview

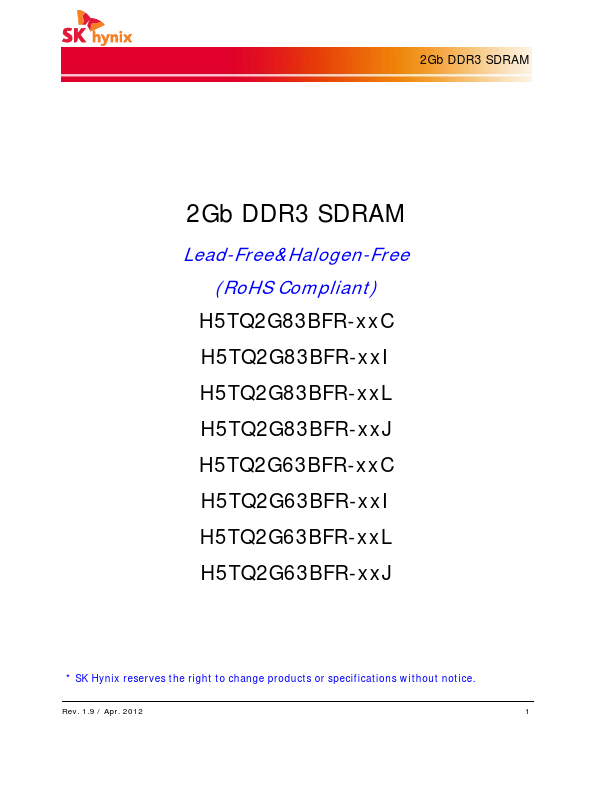

The H5TQ2G83BFR and H5TQ2G63BFR are 2,147,483,648-bit CMOS Double Data Rate III (DDR3) Synchronous DRAM, ideally suited for the main memory applications which requires large memory density and high bandwidth. SK Hynix 2Gb DDR3 SDRAMs offer fully synchronous operations referenced to both rising and falling edges of the clock.

- VDD=VDDQ=1.5V +/- 0.075V

- Fully differential clock inputs (CK, CK) operation

- Differential Data Strobe (DQS, DQS)

- On chip DLL align DQ, DQS and DQS transition with CK transition

- DM masks write data-in at the both rising and falling edges of the data strobe

- All addresses and control inputs except data, data strobes and data masks latched on the rising edges of the clock

- Programmable CAS latency 5, 6, 7, 8, 9, 10, 11, 12,