H5TQ4G83EFR

Description

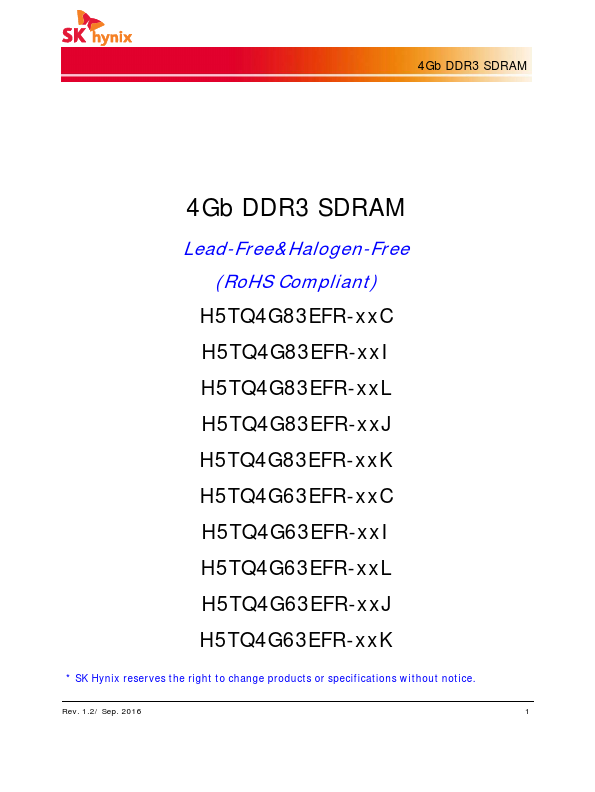

The H5TQ4G83EFR-xxC,H5TQ4G63EFR-xxC, H5TQ4G83EFR-xxI, H5TQ4G63EFR-xxI, H5TQ4G83EFR-xxL, H5TQ4G63EFR-xxL, H5TQ4G83EFR-xxJ, H5TQ4G63EFR-xxJ, H5TQ4G83EFR-xxK and H5TQ4G63EFR-xxK are a 4,294,967,296-bit CMOS Double Data Rate III (DDR3) Synchronous DRAM, ideally suited for the main memory applications which requires large memory density and high bandwidth.

Key Features

- VDD=VDDQ=1.5V +/- 0.075V

- Fully differential clock inputs (CK, CK) operation

- Differential Data Strobe (DQS, DQS)

- On chip DLL align DQ, DQS and DQS transition with CK transition

- DM masks write data-in at the both rising and falling edges of the data strobe

- All addresses and control inputs except data, data strobes and data masks latched on the rising edges of the clock

- Programmable additive latency 0, CL-1, and CL-2 supported

- Programmable burst length 4/8 with both nibble sequential and interleave mode

- BL switch on the fly

- Driver strength selected by EMRS