HC2510C

HC2510C is Phase-Locked Loop Clock Distribution for Synchronous DRAM Applications manufactured by SK Hynix.

Features l l l l l l l l l l l Phase-Locked Loop Clock Distribution for Synchronous DRAM Applications Supports PC-100 and Meets “PC100 SDRAM registered DIMM Specification Rev. 1.2” Distributes One Clock Input to One Bank of Ten Outputs No External RC Network Required External Feedback (FBIN) Pin is Used to Synchronize the Outputs to the Clock Input Separate Output Enable for Each Output Bank Operates at 3.3 V Vcc 125 MHz Maximum Frequency On-chip Series Damping Resistors Support Spread Spectrum Clock(SSC) Synthesizers ESD Protection Exceeds 3000 V per MIL-STD883, Method 3015 ; Exceeds 350 V Using Machine Model ( C = 200 p F, R = 0 ) Latch-Up Performance Exceeds 400 m A per JESD 17 Packaged in Plastic 24-Pin Thin Shrink Small Outline Package

General Description

The HC2510C is a low-skew, low jitter, phaselocked loop(PLL) clock driver, distributing high frequency clock signals for SDRAM. The HC2510C operates at 3.3V Vcc and provides integrated series-damping resistors that make it ideal for driving point-to-point loads. The propagation delay from the CLK input to any clock output is nearly zero. Ten outputs provide low-skew and low-jitter clocks. All outputs can be enabled or disabled via the control input(G). Output signal duty cycles are adjusted to 50 percent, independent of the duty cycle at CLK. The HC2510C is specially designed to interface with high speed SDRAM applications in the range of 25MHz to 125MHz and includes an internal RC network which provides excellent jitter characteristics and eliminates the needs for external ponents. For the test purpose, the PLL can be bypassed by strapping AVcc to ground. The HC2510C is characterized for operation from 0°C to 85°C. l l

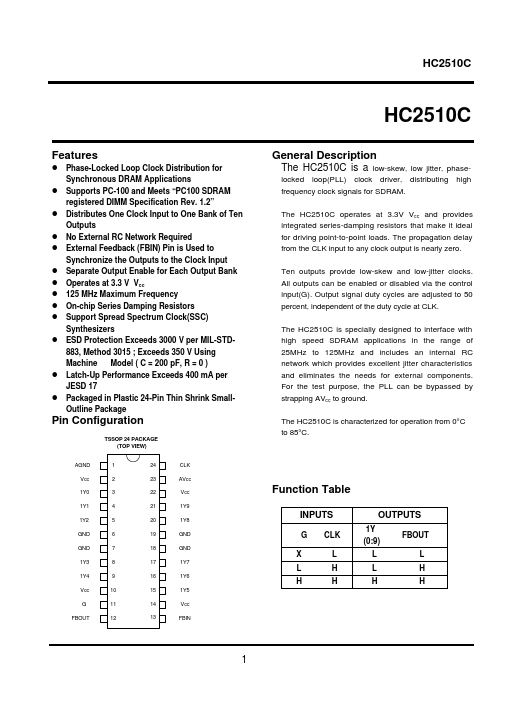

Pin Configuration

TSSOP 24 PACKAGE (TOP VIEW) AGND Vcc 1Y0 1Y1 1Y2 GND GND 1Y3 1Y4 Vcc G FBOUT 1 2 3 4 5 6 7 8 9 10 11 12 24 23 22 21 20 19 18 17 16 15 14 13 CLK AVcc Vcc 1Y9 1Y8 GND GND

Function Table

INPUTS

G X CLK L H H

OUTPUTS

1Y (0:9) L L H FBOUT L H H

1Y7

1Y6...