HY67V161610D

HY67V161610D is 2 Banks x 512K x 16 Bit Synchronous DRAM manufactured by SK Hynix.

FEATURES

- -

- Single 3.0V to 3.6V power supply

Note1)

- -

- Auto refresh and self refresh 4096 refresh cycles / 64ms Programmable Burst Length and Burst Type

- 1, 2, 4, 8 and Full Page for Sequence Burst

All device pins are patible with LVTTL interface JEDEC standard 400mil 50pin TSOP-II with 0.8mm of pin pitch

- All inputs and outputs referenced to positive edge of system clock

- 1, 2, 4 and 8 for Interleave Burst

- Programmable C A S Latency ; 1, 2, 3 Clocks

- -

Data mask function by UDQM/LDQM Internal two banks operation

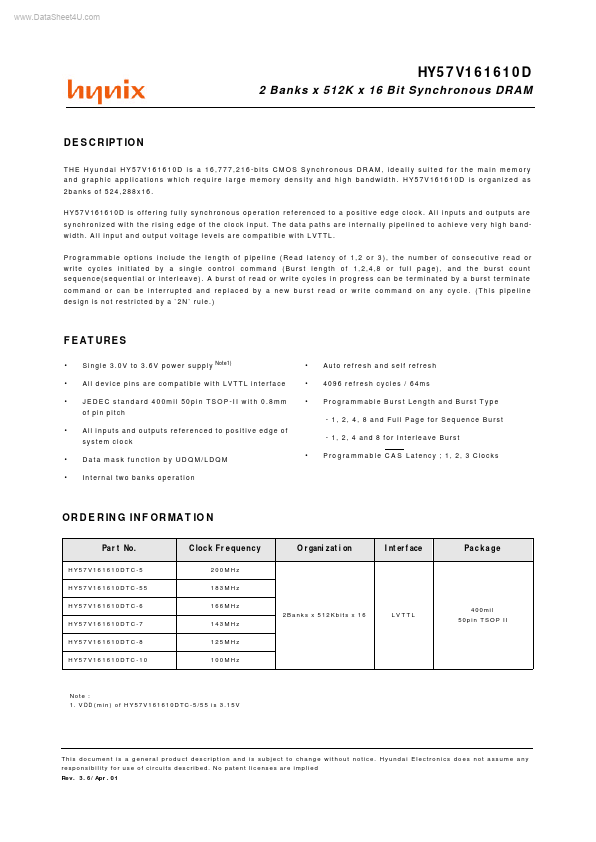

O R D E R IN G IN F O R M A T IO N

Part No.

HY57V161610DTC-5 HY57V161610DTC-55 HY57V161610DTC-6 HY57V161610DTC-7 HY57V161610DTC-8 HY57V161610DTC-10

C lo c k F r e q u e n c y

200MHz 183MHz 166MHz

O rganization

Interface

Package

2Banks x 512Kbits x 16 143MHz 125MHz 100MHz

LVTTL

400mil 50pin TSOP II

Note : 1. V DD ( m i n ) o f H Y 5 7 V 1 6 1 6 1 0 D T C

- 5 / 5 5 i s 3 . 1 5 V

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any responsibility for use of circuits described. No patent licenses are implied Rev. 3.6/Apr.01

HY57V161610D

P IN C O N F IG U R A T IO N

VDD DQ0 DQ1 VSSQ DQ2 DQ3 VDDQ DQ4 DQ5 VSSQ DQ6 DQ7 VDDQ LDQM WE CAS RAS CS A11 A10 A0 A1 A2 A3 VDD

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 50pin TSOP-II 400mil x 825mil 0.8mm pin pitch

50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26

VSS DQ15 DQ14 VSSQ DQ13 DQ12 VDDQ DQ11 DQ10 VSSQ DQ9 DQ8 VDDQ NC UDQM CLK CKE NC A9 A8 A7 A6 A5 A4 VSS

P IN D E S C R IP T IO N

PIN P I N N A M E D E S C R IPTIO N The system clock input. All other inputs are referenced to the SDRAM on the rising edge of CLK. Controls internal clock signal and when deactivated, the SDRAM will be one of the states among power down, suspend or...