AiP74HCT595

Description

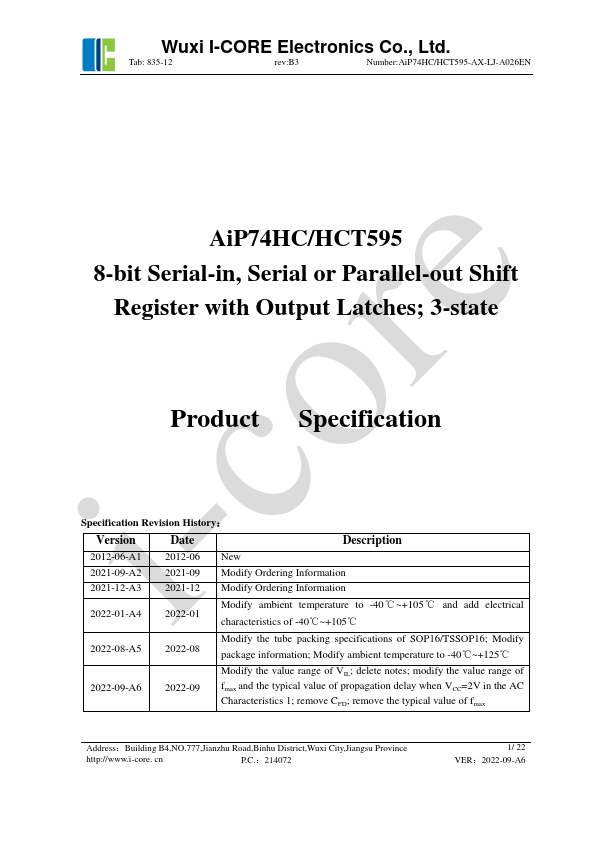

2012-06-A1 2012-06 New

2021-09-A2 2021-09 Modify Ordering Information

2021-12-A3 2021-12 Modify Ordering Information

2022-01-A4

2022-01

Modify ambient temperature to -40℃~+105℃ and add electrical characteristics of -40℃~+105℃

2022-08-A5

2022-08

Modify the tube packing specifications of SOP16/TSSOP16; Modify package information; Modify ambient temperature to -40℃~+125℃

2022-09-A6

2022-09

Modify the value range of VIL; delete notes; modify the value range of fmax and the typical value of propagation delay when VCC=2V in the AC Characteristics 1; remove CPD; remove the typical value of fmax

Address:Building B4,NO.777,Jianzhu Road,Binhu District,Wuxi City,Jiangsu Province http://.i-core. cn

P.C.:214072

1/ 22 VER:2022-09-A6

Wuxi I-CORE Electronics Co., Ltd.

Tab: 835-12 rev:B3

Number:Ai P74HC/HCT595-AX-LJ-A026EN

1、General Description

The Ai P74HC/HCT595 is an 8-bit serial-in/serial or parallel-out shift register with a storage register and

3-state outputs....