ICS487-25

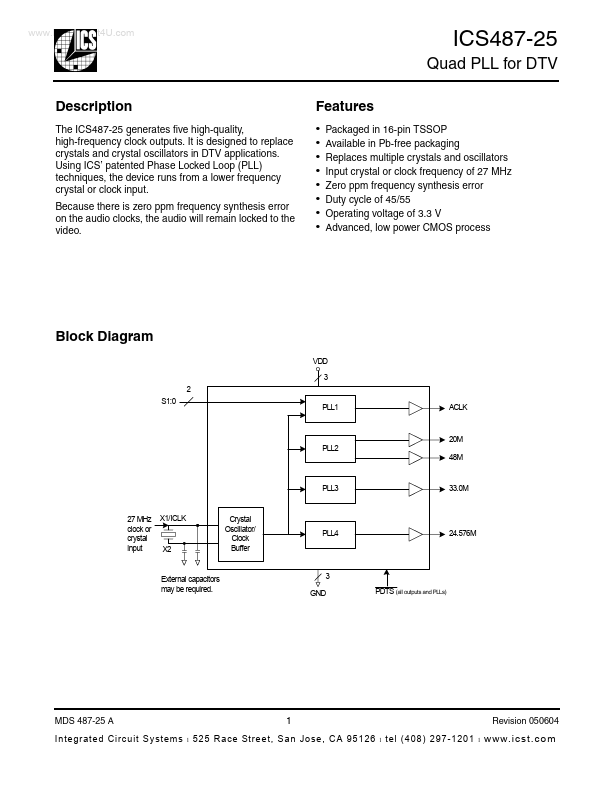

ICS487-25 is Quad PLL manufactured by ICS.

..

Quad PLL for DTV

Features

- -

- -

- -

- -

Packaged in 16-pin TSSOP Available in Pb-free packaging Replaces multiple crystals and oscillators Input crystal or clock frequency of 27 MHz Zero ppm frequency synthesis error Duty cycle of 45/55 Operating voltage of 3.3 V Advanced, low power CMOS process

Description

The ICS487-25 generates five high-quality, high-frequency clock outputs. It is designed to replace crystals and crystal oscillators in DTV applications. Using ICS’ patented Phase Locked Loop (PLL) techniques, the device runs from a lower frequency crystal or clock input. Because there is zero ppm frequency synthesis error on the audio clocks, the audio...