9DBL0443

9DBL0443 is 4-output 3.3V LP-HCSL Zero-Delay Buffer manufactured by IDT.

Description

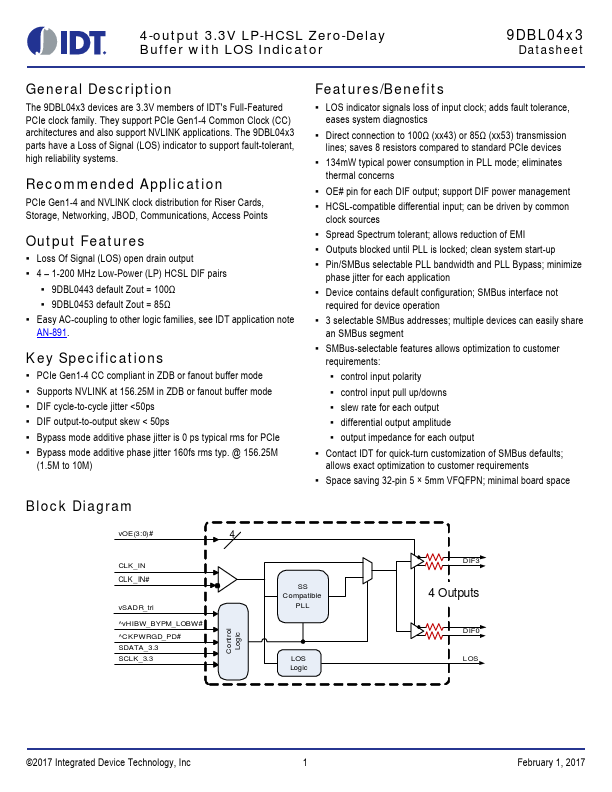

The 9DBL04x3 devices are 3.3V members of IDT's Full-Featured PCIe clock family. They support PCIe Gen1-4 mon Clock (CC) architectures and also support NVLINK applications. The 9DBL04x3 parts have a Loss of Signal (LOS) indicator to support fault-tolerant, high reliability systems.

Remended Application

PCIe Gen1-4 and NVLINK clock distribution for Riser Cards, Storage, Networking, JBOD, munications, Access Points

Output Features

- Loss Of Signal (LOS) open drain output

- 4

- 1-200 MHz Low-Power (LP) HCSL DIF pairs

- 9DBL0443 default Zout = 100Ω

- 9DBL0453 default Zout = 85Ω

- Easy AC-coupling to other logic families, see IDT application note AN-891.

Key Specifications

- PCIe Gen1-4 CC pliant in ZDB or fanout buffer mode

- Supports NVLINK at 156.25M in ZDB or fanout buffer mode

- DIF cycle-to-cycle jitter <50ps

- DIF output-to-output skew < 50ps

-...