9FGL0451 Overview

Key Specifications

Pins: 32

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Min Voltage (typical range): 3.135 V

Description

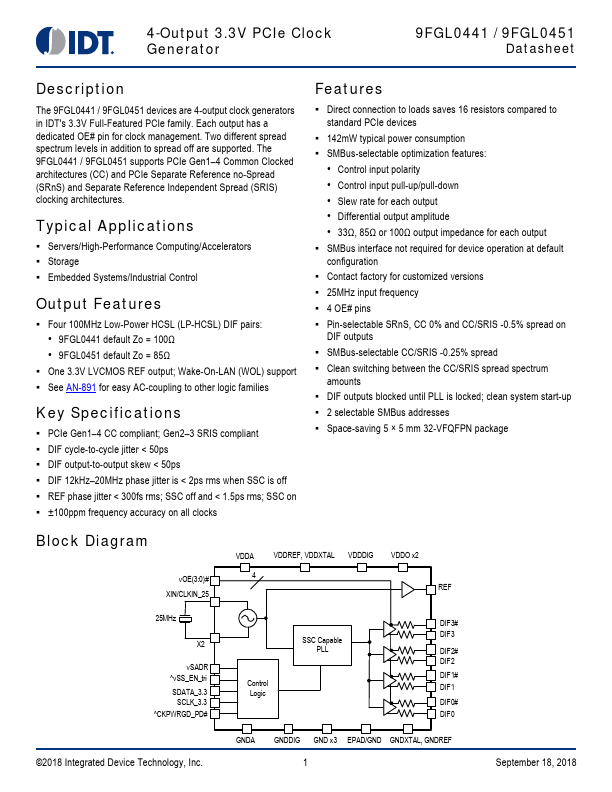

The 9FGL0441 / 9FGL0451 devices are 4-output clock generators in IDT's 3.3V Full-Featured PCIe family. Each output has a dedicated OE# pin for clock management.

Key Features

- 9FGL0441 default Zo = 100Ω