9FGL0641 Overview

Key Specifications

Mount Type: Surface Mount

Pins: 40

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Description

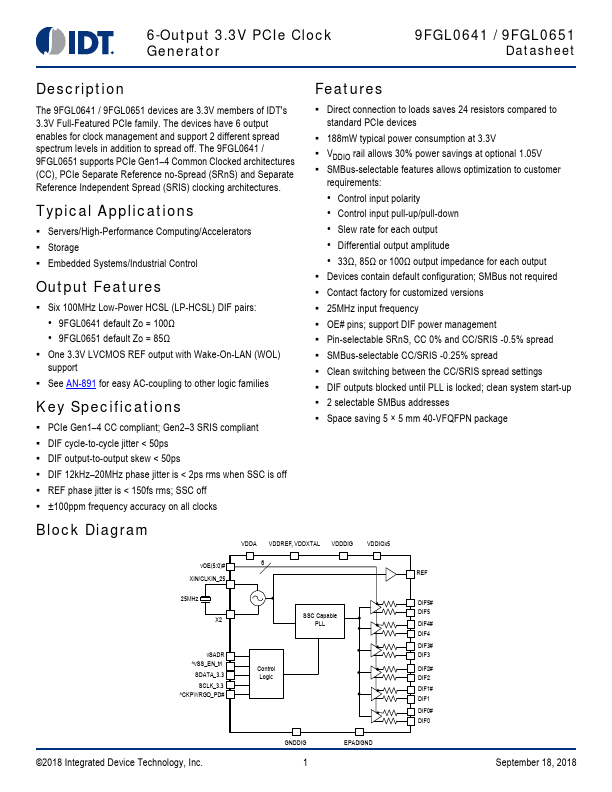

The 9FGL0641 / 9FGL0651 devices are 3.3V members of IDT's 3.3V Full-Featured PCIe family. The devices have 6 output enables for clock management and support 2 different spread spectrum levels in addition to spread off.

Key Features

- 9FGL0641 default Zo = 100Ω