9LPRS501 Overview

Key Specifications

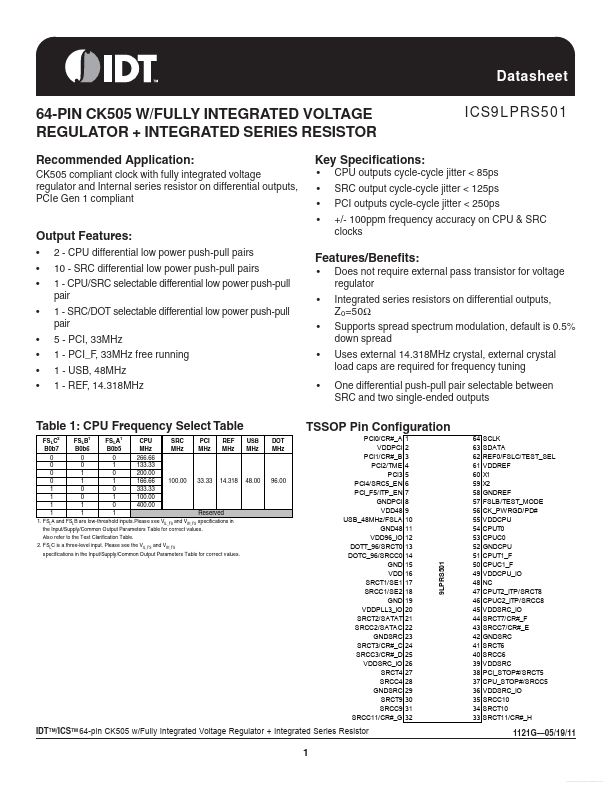

Mount Type: Surface Mount

Pins: 64

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Key Features

- Also refer to the Test Clarification Table

- FSLC is a three-level input

- Please see the VIL_FS and VIH_FS specifications in the Input/Supply/Common Output Parameters Table for correct values