IDT723654

IDT723654 is (IDT7236x4) CMOS SyncBiFIFO manufactured by IDT.

..

CMOS Sync Bi FIFOTM WITH BUS-MATCHING 2,048 x 36 x 2 4,096 x 36 x 2 8,192 x 36 x 2

IDT723654 IDT723664 IDT723674

Features

- -

- -

- -

- -

- -

- -

Memory storage capacity: IDT723654

- 2,048 x 36 x 2 IDT723664

- 4,096 x 36 x 2 IDT723674

- 8,192 x 36 x 2 Clock frequencies up to 83 MHz (8ns access time) Two independent clocked FIFOs buffering data in opposite directions Select IDT Standard timing (using EFA, EFB, FFA, and FFB flags functions) or First Word Fall Through Timing (using ORA, ORB, IRA, and IRB flag functions) Programmable Almost-Empty and Almost-Full flags; each has five default offsets (8, 16, 64, 256 and 1,024 ) Serial or parallel programming of partial flags

- -

- -

Port B bus sizing of 36 bits (long word), 18 bits (word) and 9 bits (byte) Big- or Little-Endian format for word and byte bus sizes Retransmit Capability Master Reset clears data and configures FIFO, Partial Reset clears data but retains configuration settings Mailbox bypass registers for each FIFO Free-running CLKA and CLKB may be asynchronous or coincident (simultaneous reading and writing of data on a single clock edge is permitted) Auto power down minimizes power dissipation Available in space saving 128-pin Thin Quad Flatpack (TQFP) Pin patible to the lower density parts, IDT723624/723634/723644 Industrial temperature range (- 40°C to +85°C) is available

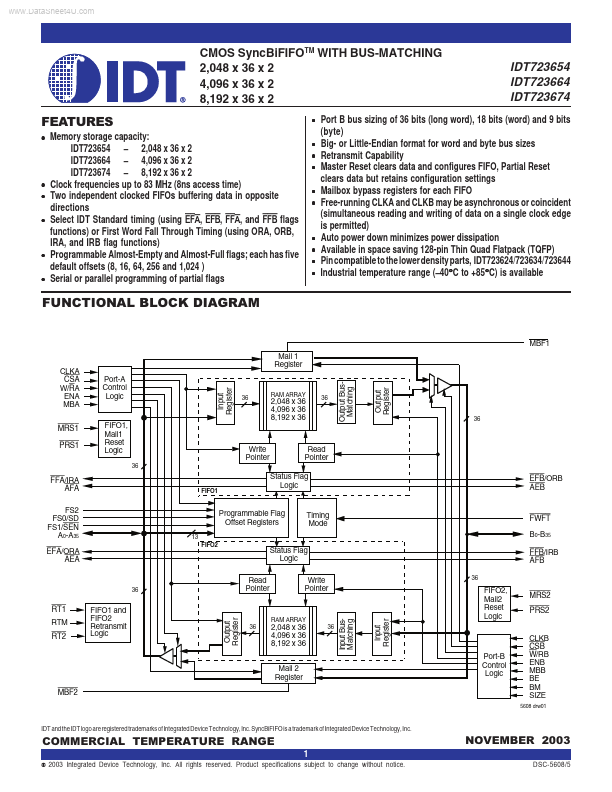

FUNCTIONAL BLOCK DIAGRAM

MBF1 Mail 1 Register

Output Bus Matching

Input Register

RAM ARRAY

2,048 x 36 4,096 x 36 8,192 x 36

Output Register

CLKA CSA W/RA ENA MBA MRS1 PRS1

Port-A Control Logic

FIFO1, Mail1 Reset Logic

Write Pointer

Read Pointer Status Flag Logic EFB/ORB AEB

FFA/IRA AFA FS2 FS0/SD FS1/SEN A0-A35 EFA/ORA...