IDT72T51553

Key Features

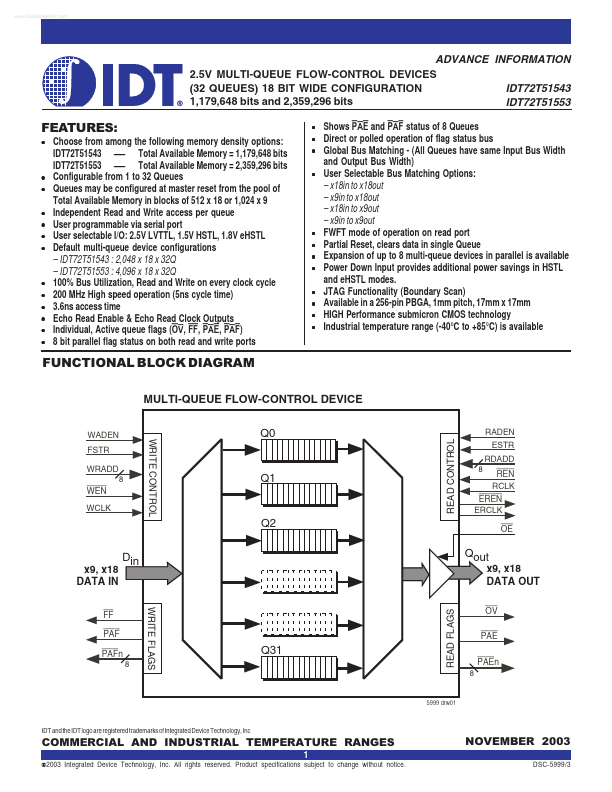

- Choose from among the following memory density options: IDT72T51543 Total Available Memory = 1,179,648 bits IDT72T51553 Total Available Memory = 2,359,296 bits Configurable from 1 to 32 Queues Queues may be configured at master reset from the pool of Total Available Memory in blocks of 512 x 18 or 1,024 x 9 Independent Read and Write access per queue User programmable via serial port User selectable I/O: 2.5V LVTTL, 1.5V HSTL, 1.8V eHSTL Default multi-queue device configurations - IDT72T51543 : 2,048 x 18 x 32Q - IDT72T51553 : 4,096 x 18 x 32Q 100% Bus Utilization, Read and Write on every clock cycle 200 MHz High speed operation (5ns cycle time) 3.6ns access time Echo Read Enable & Echo Read Clock Outputs Individual, Active queue flags (OV, FF, PAE, PAF) 8 bit parallel flag status on both read and write ports * * * * * * * * * * *

- Shows PAE and PAF status of 8 Queues Direct or polled operation of flag status bus Global Bus Matching - (All Queues have same Input Bus Width and Output Bus Width) User Selectable Bus Matching Options: - x18in to x18out - x9in to x18out - x18in to x9out - x9in to x9out FWFT mode of operation on read port Partial Reset, clears data in single Queue Expansion of up to 8 multi-queue devices in parallel is available Power Down Input provides additional power savings in HSTL and eHSTL modes. JTAG Functionality (Boundary Scan) Available in a 256-pin PBGA, 1mm pitch, 17mm x 17mm HIGH Performance submicron CMOS technology Industrial temperature range (-40°C to +85°C) is available