IDTCV125

IDTCV125 is PROGRAMMABLE FLEXPC CLOCK manufactured by IDT.

FEATURES

:

- Power management control suitable for notebook applications

- One high precision PLL for CPU, SSC and N programming

- One high precision PLL for SRC/PCI, supports 100MHz output frequency, SSC and N programming

- One high precision PLL for LVDS. Supports 100/96MHz output frequency, SSC programming

- One high precision PLL for 96MHz/48MHz

- Band-gap circuit for differential outputs

- Support spread spectrum modulation,

- 0.5 down spread and others

- Support SMBus block read/write, index read/write

- Selectable output strength for REF

- Allows for CPU frequency to change to a slower frequency to conserve power when an application is less executionintensive

- Smooth transition for N programming

- Available in TSSOP package

IDTCV125 is a 56 pin clock device, incorporating both Intel CK410M and CKSSCD requirements, for Intel advance P4 processors. The CPU output buffer is designed to support up to 400MHz processor. This chip has four PLLs inside for CPU, SRC/PCI, LVDS, and 48MHz/DOT96 IO clocks. This device also implements Band-gap referenced IREF to reduce the impact of VDD variation on differential outputs, which can provide more robust system performance. Static PLL frequency divide error can be as low as 36 ppm, worse case 114 ppm, providing high accuracy output clock. Each CPU/SRC/LVDS has its own Spread Spectrum selection.

DESCRIPTION

:

OUTPUTS:

- -

- -

- -

- KEY SPECIFICATION:

- -

- -

2- 0.7V current

- mode differential CPU CLK pair 6- 0.7V current

- mode differential SRC CLK pair One CPU_ITP/SRC selectable CLK pair 6- PCI, 2 free running, 33.3MHz 1- 96MHz, 1- 48MHz 1- REF One 100/96 MHz differential LVDS

CPU/SRC CLK cycle to cycle jitter < 85ps PCI CLK cycle to cycle jitter < 250ps Static PLL frequency divide error < 114 ppm Static PLL frequency divide error for 48MHz < 5 ppm

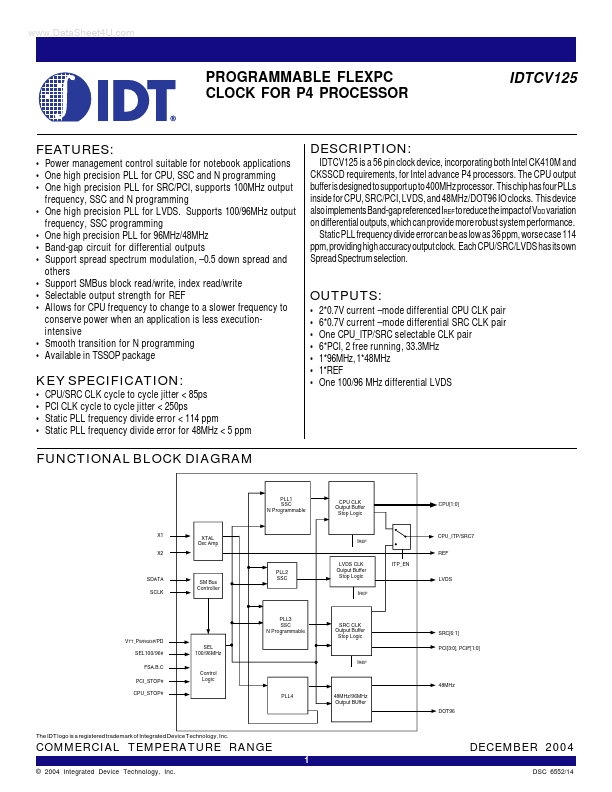

FUNCTIONAL BLOCK DIAGRAM

PLL1 SSC N Programmable

CPU CLK Output Buffer Stop Logic

CPU[1:0]

X1

XTAL Osc Amp

CPU_ITP/SRC7 IREF REF LVDS CLK Output Buffer Stop Logic ITP_EN...