IN74ACT112

IN74ACT112 is Dual J-K Negative-Edge-Triggered Flip-Flop manufactured by IK Semiconductor.

TECHNICAL DATA

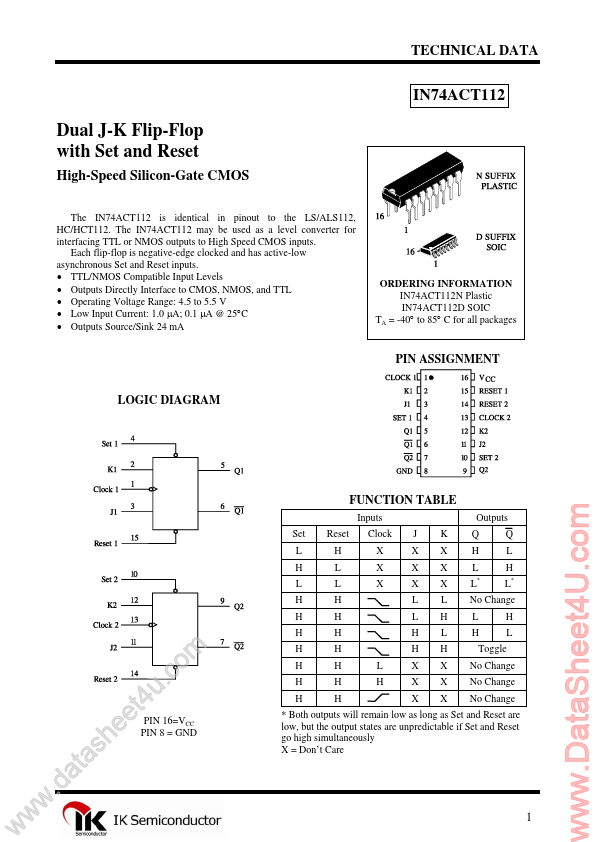

Dual J-K Flip-Flop with Set and Reset

High-Speed Silicon-Gate CMOS

The IN74ACT112 is identical in pinout to the LS/ALS112, HC/HCT112. The IN74ACT112 may be used as a level converter for interfacing TTL or NMOS outputs to High Speed CMOS inputs. Each flip-flop is negative-edge clocked and has active-low asynchronous Set and Reset inputs.

- TTL/NMOS patible Input Levels

- Outputs Directly Interface to CMOS, NMOS, and TTL

- Operating Voltage Range: 4.5 to 5.5 V

- Low Input Current: 1.0 µA; 0.1 µA @ 25°C

- Outputs Source/Sink 24 m A

ORDERING INFORMATION IN74ACT112N Plastic IN74ACT112D SOIC TA = -40° to 85° C for all packages

PIN ASSIGNMENT

LOGIC DIAGRAM

Inputs Set L H L H H H Reset H L L H H H H H H H L H Clock X X X J X X X L L H H X X X K X X X L H L H X X X

Outputs Q H L L

- Q L H L- H L

No Change L H w w w

.d h s a t a ee

. u t4 m o c

Toggle No Change No Change No Change

PIN 16=VCC PIN 8 = GND

- Both outputs will remain low as long as Set and Reset are low, but the output states are unpredictable if Set and Reset go high simultaneously X = Don’t Care

..

FUNCTION TABLE

MAXIMUM RATINGS-

Symbol VCC VIN VOUT IIN IOUT ICC PD Tstg TL

- Parameter DC Supply Voltage (Referenced to GND) DC Input Voltage (Referenced to GND) DC Output Voltage (Referenced to GND) DC Input Current, per Pin DC Output Sink/Source Current, per Pin DC Supply Current, VCC and GND Pins Power Dissipation in Still Air, Plastic DIP+ SOIC Package+ Storage Temperature Lead Temperature, 1 mm from Case for 10 Seconds (Plastic DIP or SOIC Package)

Value -0.5 to +7.0 -0.5 to VCC +0.5 -0.5 to VCC +0.5 ±20 ±50 ±50 750 500 -65 to +150 260

Unit V V V m A m A m A m W °C °C

Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Remended Operating Conditions. +Derating

- Plastic DIP:

- 10 m W/°C from 65° to 125°C SOIC Package: :

- 7 m W/°C from 65° to 125°C

REMENDED OPERATING...