IS42VS83200J

Description

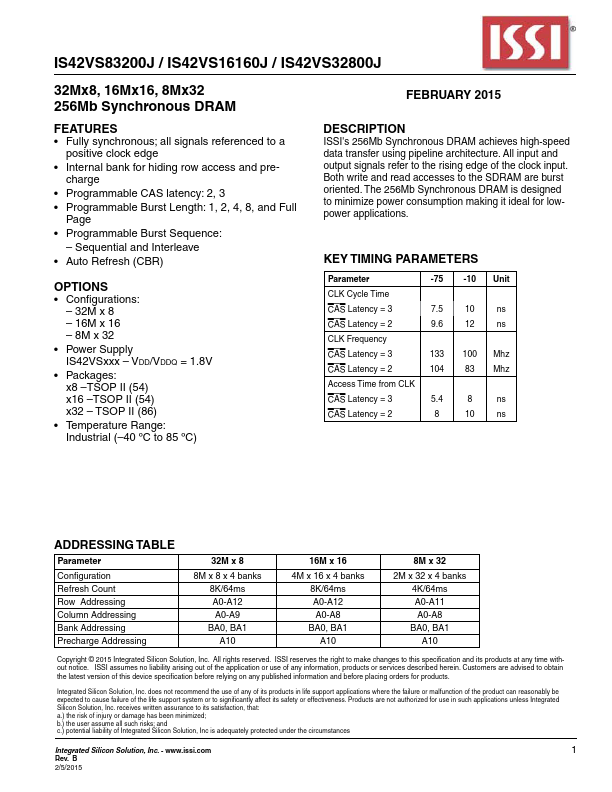

ISSI's 256Mb Synchronous DRAM achieves high-speed data transfer using pipeline architecture. All input and output signals refer to the rising edge of the clock input.

Key Features

- Fully synchronous; all signals referenced to a positive clock edge

- Internal bank for hiding row access and pre- charge

- Programmable CAS latency: 2, 3

- Programmable Burst Length: 1, 2, 4, 8, and Full Page

- Programmable Burst Sequence: - Sequential and Interleave

- Auto Refresh (CBR) OPTIONS

- Configurations: - 32M x 8 - 16M x 16 - 8M x 32

- Power Supply IS42VSxxx - Vdd/Vddq = 1.8V

- Packages: x8 -TSOP II (54) x16 -TSOP II (54) x32 - TSOP II (86)

- Temperature Range: Industrial (-40 ºC to 85 ºC)