IS43LD16640A

IS43LD16640A is 1Gb Mobile LPDDR2 S4 SDRAM manufactured by ISSI.

- Part of the IS46LD16640A comparator family.

- Part of the IS46LD16640A comparator family.

FEATURES

- Low-voltage Core and I/O Power Supplies VDD2 = 1.14-1.30V, VDDCA/VDDQ = 1.14-1.30V, VDD1 = 1.70-1.95V

- High Speed Un-terminated Logic(HSUL_12) I/O Interface

- Clock Frequency Range : 10MHz to 400MHz (data rate range : 20Mbps to 800 Mbps per I/O)

- Four-bit Pre-fetch DDR Architecture

- Multiplexed, double data rate, mand/address inputs

- Eight internal banks for concurrent operation

- Bidirectional/differential data strobe per byte of data (DQS/DQS#)

- Programmable Read/Write latencies(RL/WL) and burst lengths(4,8 or 16)

- Per-bank refresh for concurrent operation

- ZQ Calibration

- On-chip temperature sensor to control self refresh rate

- Partial

- array self refresh(PASR)

- Bank & Segment masking

- Deep power-down mode(DPD)

- Operation Temperature mercial (TC = 0°C to 85°C) Industrial (TC = -40°C to 85°C) Automotive, A1 (TC = -40°C to 85°C) Automotive, A2 (TC = -40°C to 105°C)

OPTIONS

- Configuration:

- 64Mx16 (8M x 16 x 8 banks)

- 32Mx32 (4M x 32 x 8 banks) Package:

- 134-ball BGA for x16 / x32

- 168-ball Po P BGA for x32 description

The IS43/46LD16640A/32320A is 1,073,741,824 bits CMOS Mobile Double Data Rate Synchronous DRAMs organized as 8 banks (S4). The deviceis organized as 8 banks of 8Meg words of 16bits or 4Meg words of 32bits. This product uses a double-data-rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 4N prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. This product offers fully synchronous operations referenced to both rising and falling edges of the clock. The data paths are internally pipelined and 4n bits prefetched to achieve very high bandwidth.

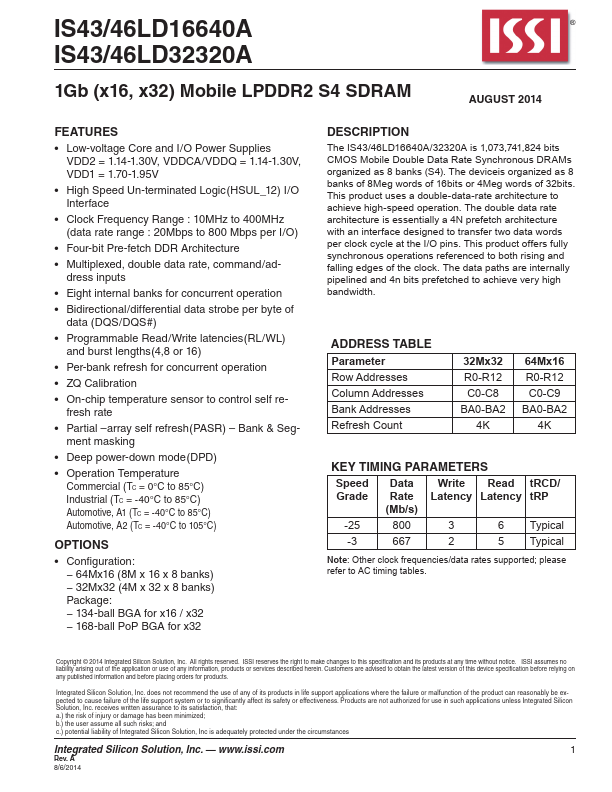

ADDRESS TABLE

Parameter Row Addresses Column Addresses Bank Addresses Refresh Count

32Mx32 R0-R12 C0-C8 BA0-BA2

4K

64Mx16 R0-R12 C0-C9 BA0-BA2

4K k EY TIMING PARAMETERS

Speed Grade

-25 -3

Data Rate (Mb/s)

Write Read t RCD/ Latency Latency t RP

3 6 Typical...