IS45S32800L

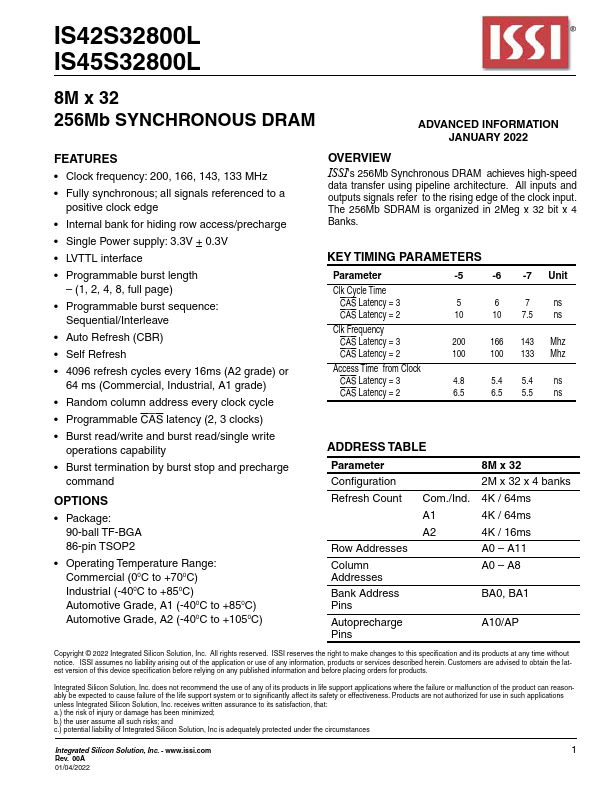

IS45S32800L is 8M x 32 256Mb SYNCHRONOUS DRAM manufactured by ISSI.

- Part of the IS42S32800L comparator family.

- Part of the IS42S32800L comparator family.

FEATURES

- Clock frequency: 200, 166, 143, 133 MHz

- Fully synchronous; all signals referenced to a positive clock edge

- Internal bank for hiding row access/precharge

- Single Power supply: 3.3V + 0.3V

- LVTTL interface

- Programmable burst length

- (1, 2, 4, 8, full page)

- Programmable burst sequence:

Sequential/Interleave

- Auto Refresh (CBR)

- Self Refresh

- 4096 refresh cycles every 16ms (A2 grade) or

64 ms (mercial, Industrial, A1 grade)

- Random column address every clock cycle

- Programmable CAS latency (2, 3 clocks)

- Burst read/write and burst read/single write operations capability

- Burst termination by burst stop and precharge mand

OPTIONS

- Package:

90-ball TF-BGA 86-pin TSOP2

- Operating Temperature Range: mercial (0o C to +70o C) Industrial (-40o C to +85o C) Automotive Grade, A1 (-40o C to +85o C) Automotive Grade, A2 (-40o C to +105o C)

OVERVIEW

ISSI's 256Mb Synchronous DRAM achieves high-speed data transfer using pipeline architecture. All inputs and outputs signals refer to the rising edge of the clock input. The 256Mb SDRAM is organized in 2Meg x 32 bit x 4 Banks.

KEY TIMING PARAMETERS

Parameter

-5

-6 -7 Unit

Clk Cycle Time CAS Latency = 3 CAS Latency = 2

7 ns

10 7.5 ns

Clk Frequency CAS Latency = 3 CAS Latency = 2

200 166 143 Mhz 100 100 133 Mhz

Access Time from Clock

CAS Latency = 3

5.4 5.4...