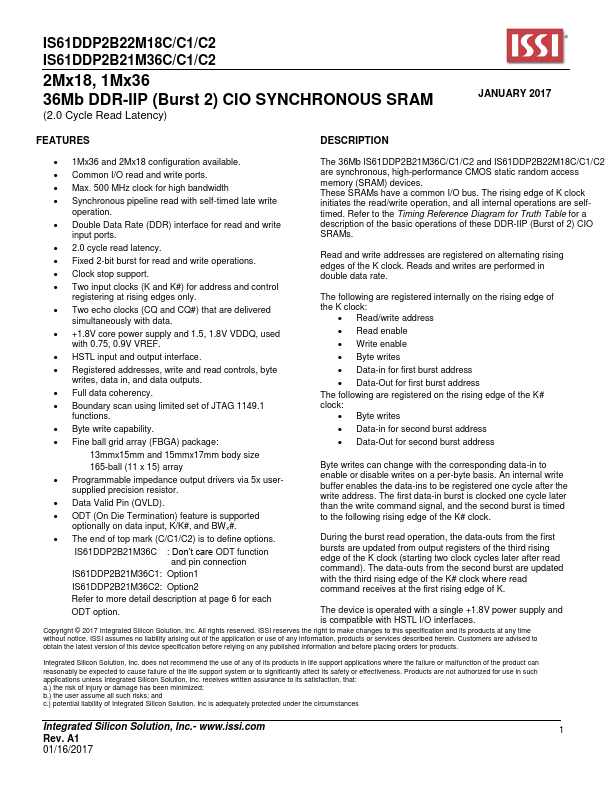

| Part | IS61DDP2B21M36C |

|---|---|

| Description | 36Mb DDR-IIP CIO SYNCHRONOUS SRAM |

| Manufacturer | ISSI |

| Size | 852.80 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| IS61DDP2B21M36A1 | ISSI | 36Mb DDR-IIP (Burst 2) CIO SYNCHRONOUS SRAM |

| IS61DDP2B21M36A | ISSI | 36Mb DDR-IIP (Burst 2) CIO SYNCHRONOUS SRAM |

| IS61DDP2B21M36A2 | ISSI | 36Mb DDR-IIP (Burst 2) CIO SYNCHRONOUS SRAM |