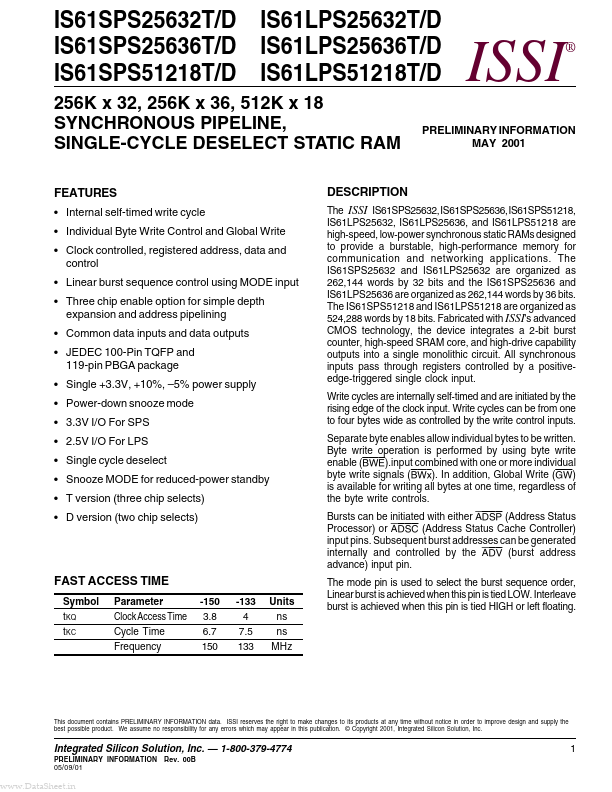

IS61SPS25636T

Overview

- Internal self-timed write cycle

- Individual Byte Write Control and Global Write

- Clock controlled, registered address, data and control

- Linear burst sequence control using MODE input

- Three chip enable option for simple depth expansion and address pipelining

- Common data inputs and data outputs

- JEDEC 100-Pin TQFP and 119-pin PBGA package

- Single +3.3V, +10%, -5% power supply

- Power-down snooze mode

- 3.3V I/O For SPS