IXTH36P10

IXTH36P10 is Standard Power MOSFET manufactured by IXYS.

Advance Technical Information

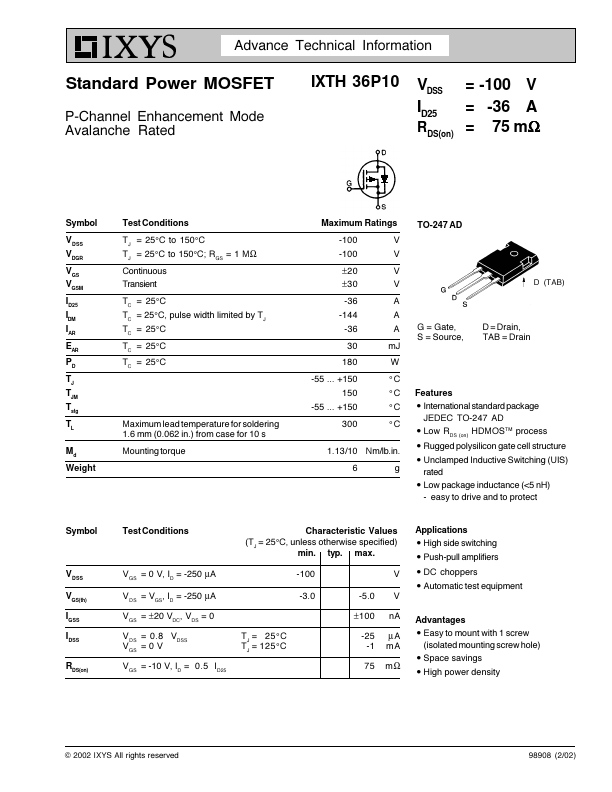

Standard Power MOSFET

P-Channel Enhancement Mode Avalanche Rated

IXTH 36P10

VDSS

ID25

RDS(on)

= -100 V = -36 A = 75 mΩ

Symbol

VDSS VDGR VGS VGSM I

D25

IAR EAR PD T

T JM

Tstg TL

M d

Weight

Test Conditions TJ = 25°C to 150°C TJ = 25°C to 150°C; RGS = 1 MΩ Continuous Transient TC = 25°C TC = 25°C, pulse width limited by TJ TC = 25°C TC = 25°C TC = 25°C

Maximum lead temperature for soldering 1.6 mm (0.062 in.) from case for 10 s Mounting torque

Maximum Ratings

-100

-100

±20

±30

-36

-144

-36

30 m J

-55 ......