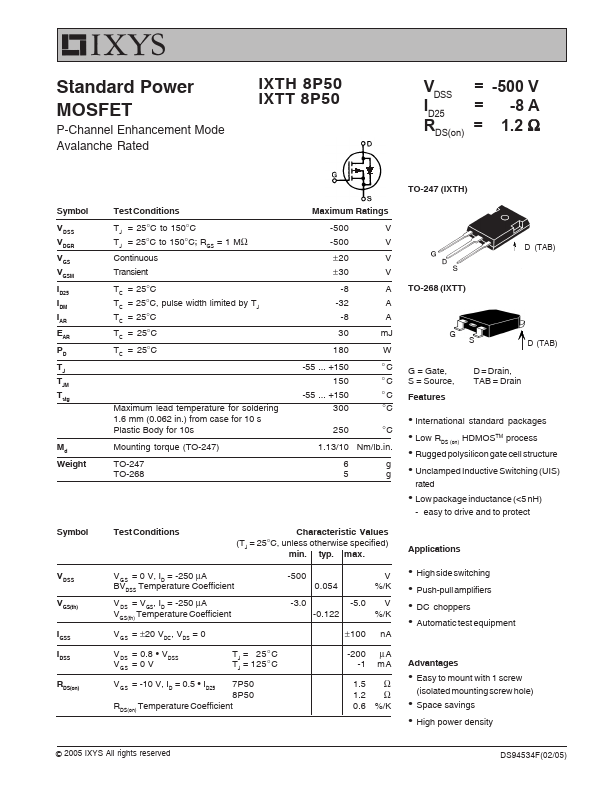

IXTH8P50 Description

+150 °C 300 °C 250 °C 1.13/10 Nm/lb.in. 6 g 5 g TO-268 (IXTT) D (TAB) GS D (TAB) G = Gate, S = Source, D = Drain, TAB = Drain.

IXTH8P50 Key Features

- International standard packages

- Low RDS (on) HDMOSTM process

- Rugged polysilicon gate cell structure

- Unclamped Inductive Switching (UIS)

- Low package inductance (<5 nH)

- easy to drive and to protect

- 500 0.054

- 200 -1