M2082

Overview

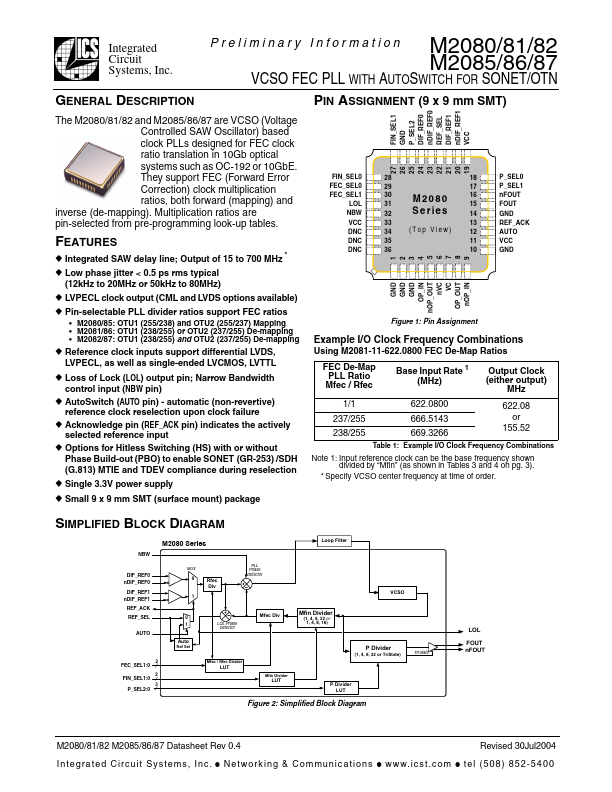

The M2080/81/82 and M2085/86/87 are VCSO (Voltage Controlled SAW Oscillator) based clock PLLs designed for FEC clock ratio translation in 10Gb optical systems such as OC-192 or 10GbE. They support FEC (Forward Error Correction) clock multiplication ratios, both forward (mapping) and inverse (de-mapping).

- Integrated SAW delay line; Output of 15 to 700 MHz *

- Low phase jitter < 0.5 ps rms typical (12kHz to 20MHz or 50kHz to 80MHz)

- LVPECL clock output (CML and LVDS options available)

- Pin-selectable PLL divider ratios support FEC ratios

- M2080/85: OTU1 (255/238) and OTU2 (255/237) Mapping

- M2081/86: OTU1 (238/255) or OTU2 (237/255) De-mapping

- M2082/87: OTU1 (238/255) and OTU2 (237/255) De-mapping