41C16256 Overview

Key Specifications

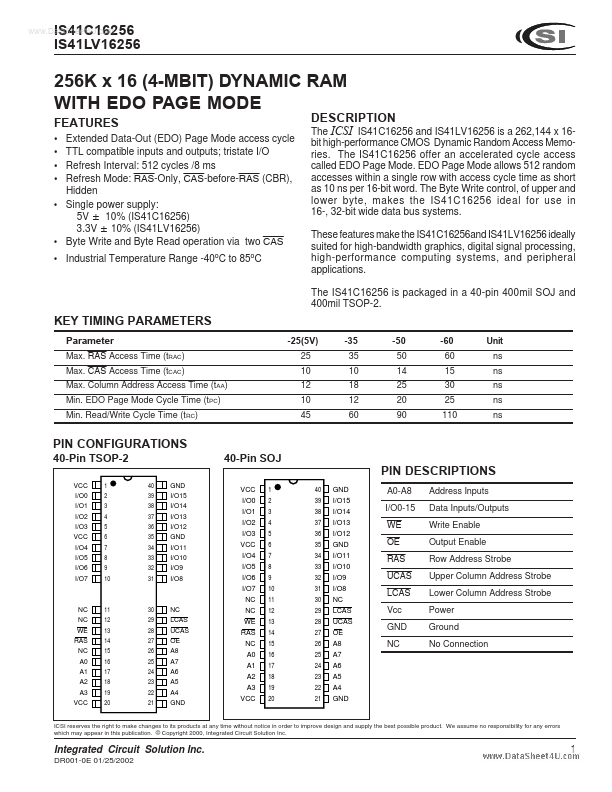

Package: TSOP

Pins: 40

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Description

The ICSI IS41C16256 and IS41LV16256 is a 262,144 x 16bit high-performance CMOS Dynamic Random Access Memories. The IS41C16256 offer an accelerated cycle access called EDO Page Mode.

Key Features

- Industrial Temperature Range -40oC to 85oC