ICS507-xx

ICS507-xx is PECL Clock Synthesizer manufactured by Integrated Circuit Systems.

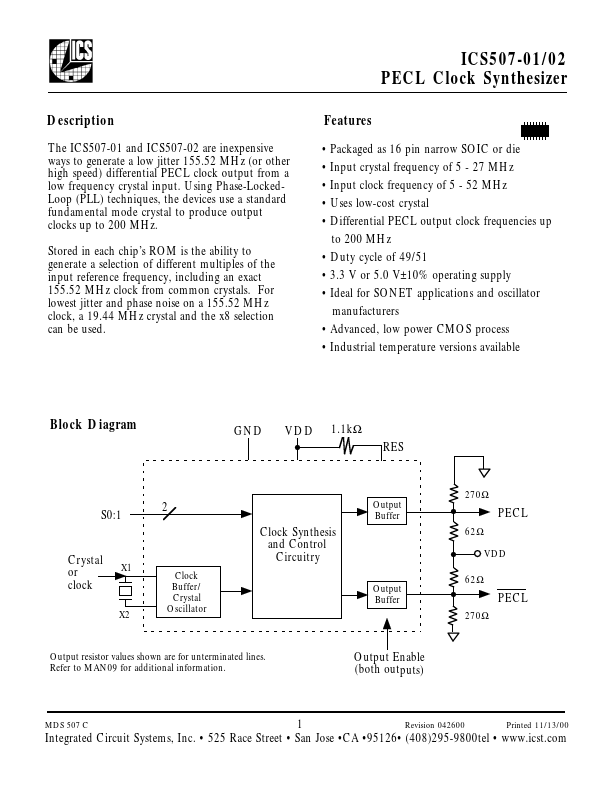

ICS507-01/02 PECL Clock Synthesizer

Description

The ICS507-01 and ICS507-02 are inexpensive ways to generate a low jitter 155.52 MHz (or other high speed) differential PECL clock output from a low frequency crystal input. Using Phase-LockedLoop (PLL) techniques, the devices use a standard fundamental mode crystal to produce output clocks up to 200 MHz. Stored in each chip’s ROM is the ability to generate a selection of different multiples of the input reference frequency, including an exact 155.52 MHz clock from mon crystals. For lowest jitter and phase noise on a 155.52 MHz clock, a 19.44 MHz crystal and the x8 selection can be used.

Features

- Packaged as 16 pin narrow SOIC or die

-...